Diseño Lógico 2

| Sección | Nombre | Descripción |

|---|---|---|

| Cartelera | ||

| Teóricos | Clase introductoria a la tecnología de los FPGAs y catalogo de productos de Xilinx. |

|

Introducción a VHDL |

||

Proceso de diseño de circuitos digitales |

||

Depuración de errores |

||

Transparencias de clase |

||

Opciones para interconexión de cores IP |

||

En caso de que al querer clonar un repo de el mensaje: "SSL certificate has expired" git config --global http.sslVerify "false" |

||

| Laboratorios | Practica 1Objetivos

Descripción general del problemaImplementar un contador de segundos. La cuenta se desplegará en los display de 7 segmentos y se podrá volver a 0 mediante uno de los pulsadores de la placa. |

|

Práctica 2Objetivos

Descripción general del problemaDiseñar el control para un sistema con un contador de segundos y un cronómetro. |

||

Práctica 3Objetivos

Descripción general del problemaModificar el cirtuito de la práctica anterior utilizando divisores que no son potencia de 2: Yn = 1/3 Xn + 1/5 Xn-1 + 1/7 Xn-2 + 1/7 Xn-3 Analizar los reportes del análisis de temporización de Altera y utilizar técnicas de pipeline para mejorar la frecuencia máxima del circuito.

|

||

Práctica 4Objetivos

Descripción general del problemaEl sistema a diseñar permitirá, desde un PC, escribir y leer varios dispositivos esclavo conectados a un bus Wishbone.Para esto se utilizará un IP Core que recibe comandos a través de la conexión JTAG y los traduce en ciclos Wishbone. |

||

| Material de apoyo | En el ejemplo se muestra como hacer un diseño, partiendo el problema en varios módulos escritos en VHDL El ejemplo implementa un bloque con 2 entradas (A[7..0], B[7..0]) que son registradas en los flancos ascendentes de CLK ( en caso de que ENA=1). |

|

El presente recurso ilustra en una forma muy básica y guiada, como crear un proyecto utilizando el Quartus II de Altera, compilarlo y simularlo. |

||

El archivo corresponde a un proyecto que tiene una entidad REGISTRO de ancho 8. El proyecto contiene simulación y asignación de dispositivo. El archivo fue generado utilizando la función Archivar proyecto del Quartus II de Altera. |

||

Archivos con hojas de datos y manuales |

||

Ayuda de Maxplus2. Vean Project Reliability Guidelines. |

||

Links con información de interes (VHDL, FPGAs, IP-Cores, etc.) |

||

Especificación y nota de aplicación de estándares de interconexión |

||

JTAG a Wishbone Master | Diseño de referenciaSystem Console se puede lanzar directamente de linea de comando: C:\altera\13.1\quartus\sopc_builder\bin\system-console.exe Si da un error Cannot load ...... jvm.dll hay que copiar el archivo MSVCR71.DLL desde $QUARTUS_ROOTDIR/bin/jre/bin/MSVCR71.DLL a $QUARTUS_ROOTDIR/bin/MSVCR71.DLL. |

||

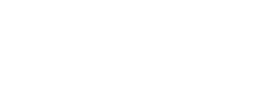

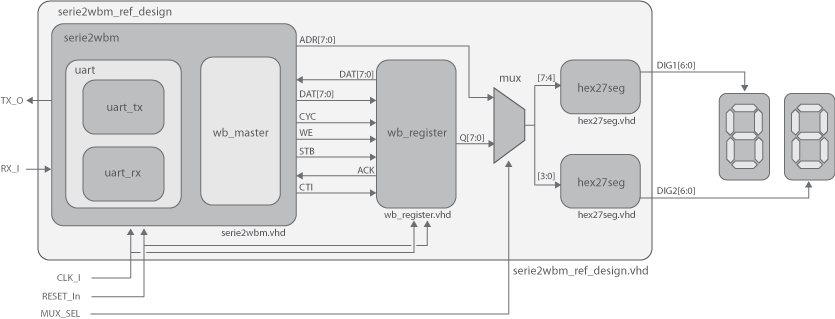

Serie a Wishbone Master | Diseño de referenciaDescripción generalEl diseño serie2wbm_ref_design es un diseño de referencia que permite experimentar con diseños con interfaz wishbone y con el diseño serie2wbm.El diseño esta pensado para ser utilizado en la placa UP1 de altera (chip EPF10K20RC240-4) y contiene:

Detalle de algunas entidadesserie2wbmDescripcion : Modulo Serie 8N1 a WB MasterEl WM Master realiza ciclos Wishbone de Lectura o Escritura simple a la dirección contenida en registro interno. Protocolo de comunicación y control a través del puerto serie:

Entidades que componen el diseño:

Generics: BAUD_RATE_16x_COUNTER_REFERENCE

SimulaciónPara simular el diseño de referencia y diseños que utilicen el bloque serie2wbm se sugiere:

Archivos disponiblessim_AddressSet_WriteByte_ReadByte.vwf: Vector para simulaciónvhdl.zip: archivos VHDL: serie2wbm_ref_design.vhd, serie2wbm.vhd, wb_register.vhd y hex27seg.vhd pin_assignament.txt: lineas a agregar en archivo .QSF para asignar pines rápidamente. |

||

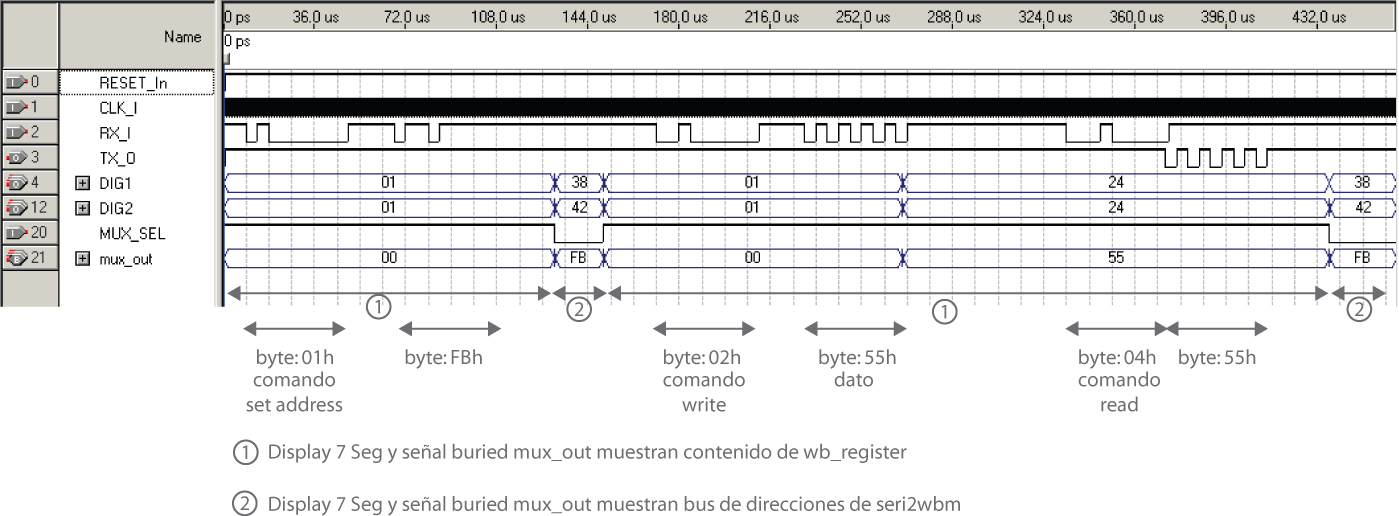

Herramientas comunicación serieConversor RS232-TTL utilizado en el cursoSeñales Archivos de diseñoEl circuito fue diseñado con el software CAD Eagle versión 5.Al pié de página puede encontrarse:

SoftwareHercules utilitySoftware que permite comunicarse en en forma serie con una aplicación. Permite enviar y recibir archivos, caracteres ASCII y hexa, etc.El software esta disponible al pie de la página y en el sitio web del desarrollador. Bray++ TerminalOtro programa emulador de terminal similar al anterior.Es solo un ejecutable, no hace falta instalar. Se puede descargar en: http://hw-server.com/software/termv19b.html |

||

Ejemplos de hardware, software y documentación sobre el procesador T80. |

||

Proyecto utilizado en clase de In System Memory |

||

Falta crear entidad ramwiz |

||

| Topic 10 | Horarios, ganancia, etc. |

|

| Topic 11 | Punteo clase inicial |