# Estándares para interconexión de cores en SOC

#### Diseño Lógico II

Instituto de Ingeniería Eléctrica Facultad de Ingeniería Universidad de la República 2019

#### Introducción

Para interconectar 2 diseños se deben definir:

- Interfaces (cantidad de señales, nombres)

- handshake para control de flujo

- protocolo de comunicación

- comportamiento de señales de interfaz

#### Importancia de los estándares

- Asegura compatibilidad entre diseños

- Acorta tiempos de diseños

- Facilita la reusabilidad de diseños

- Facilita la especificación de un diseño

#### Algunas opciones

- AVALON (Altera). Propietario

- AMBA (ARM). Abierto, usado por ARM, Altera Xilinx.

- WISHBONE (Silicore Corporation). Abierto

#### **AVALON**

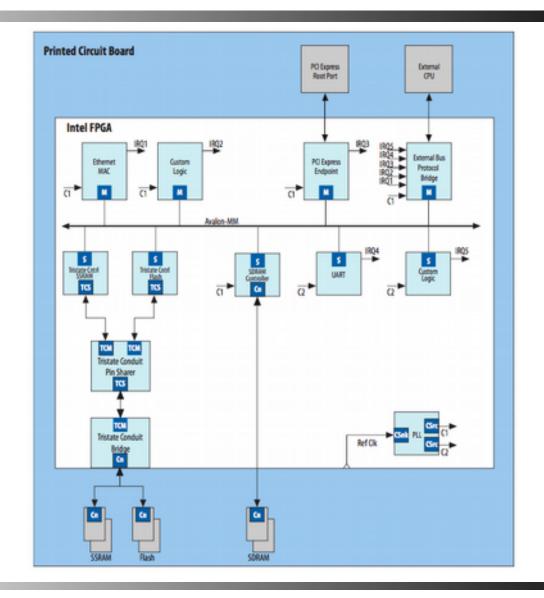

- Desarrollado por ALTERA.

- última revisión: 2017-05-08

- Define señales, su comportamiento, señalización de errores y tipos de transferencias entre periféricos y un "switch de interconexión"

- Multi-master, multi-slave

- Switch de inteconexión generado por wizard de Altera

# AVALON | sistema típico

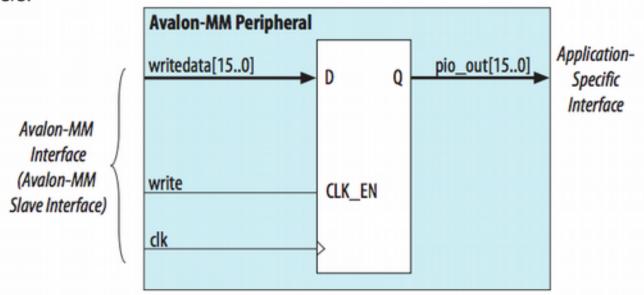

#### AVALON | ejemplo sencillo

#### **Example Slave Component**

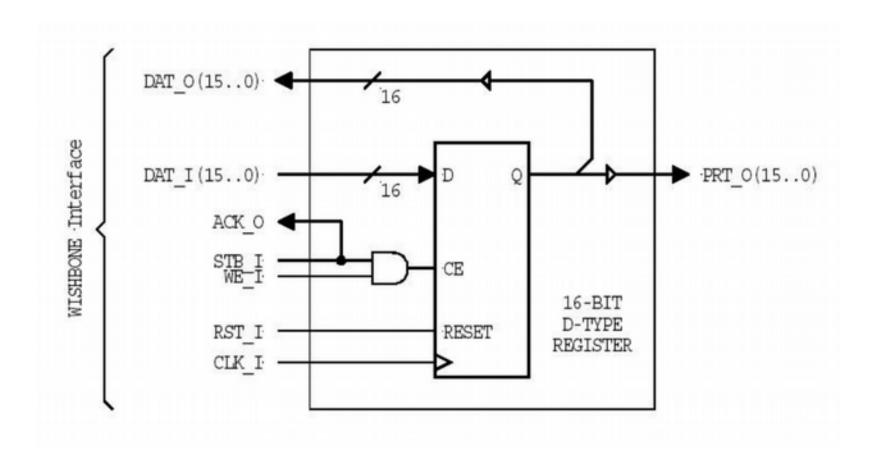

The 16-bit general-purpose I/O peripheral shown in the following figure only responds to write requests. This component includes only the slave signals required for write transfers.

Each signal in an Avalon-MM slave corresponds to exactly one Avalon-MM signal role. An Avalon-MM interface can use only one instance of each signal role.

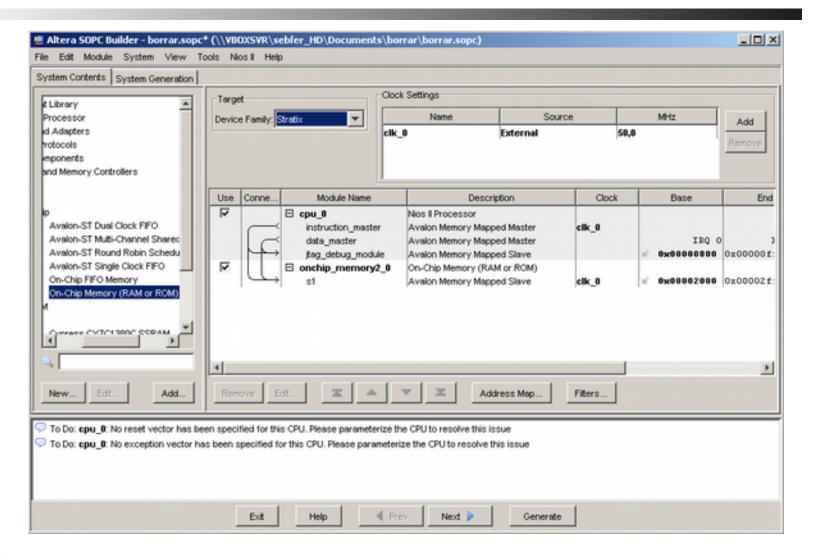

#### **AVALON** | Wizard

#### Wishbone

- Desarrollado por Silicore Corporation

- última revisión: B4 (2010)

- Recomendada por Opencores

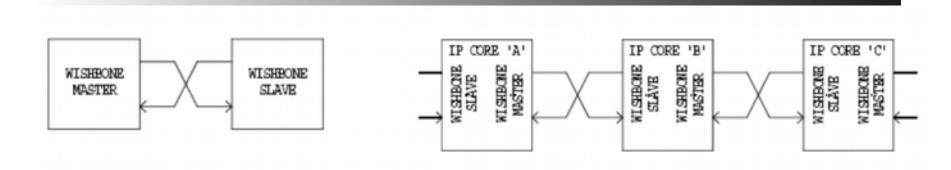

- Define interfaces, deja libre las formas de interconexión.

- No especifica funcionamiento del Core.

- Orientado a arquitectura Maestro/Esclavo.

- No hay pines bidireccionales.

- Handshake para regular velocidad de la comunicación.

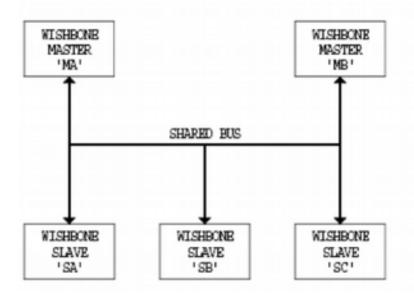

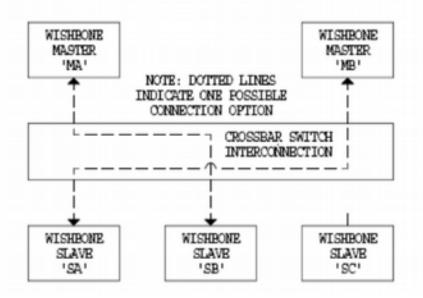

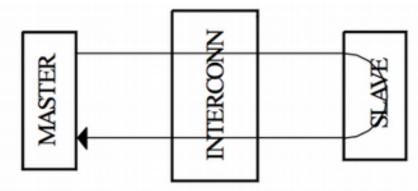

# Wishbone | sistemas típicos

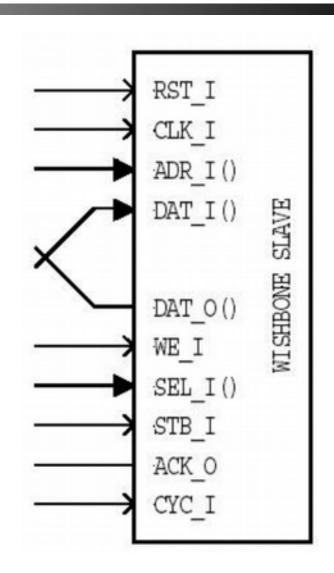

#### Wishbone | señales interfaz

#### Esclavo

- RST\_I y CLK\_I

- DAT\_I() y DAT\_O()

- ADR\_I() y SEL\_I()

- CYC\_I y WE\_I

- ACK\_O, ERR\_O, RTY\_O

- LOCK\_I

- STB\_I

- TGn\_I()

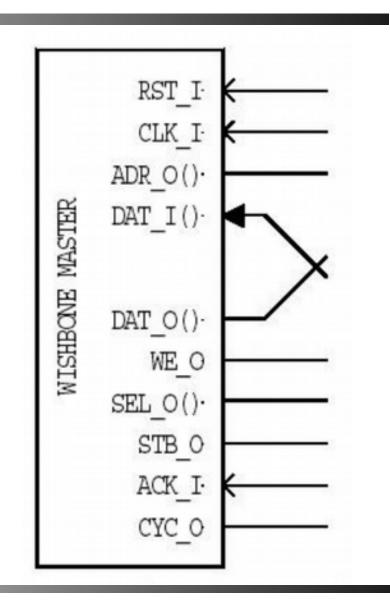

#### Wishbone | señales interfaz

#### Maestro

- RST\_I y CLK\_I

- DAT\_I() y DAT\_O()

- ADR\_O() y SEL\_O()

- CYC\_O y WE\_O

- ACK\_I, ERR\_I, RTY\_I

- LOCK\_O

- STB\_O

- TGn\_O()

#### Wishbone | ciclos

- Reset

- READ/WRITE simple

- RMW

- READ/WRITE en bloque

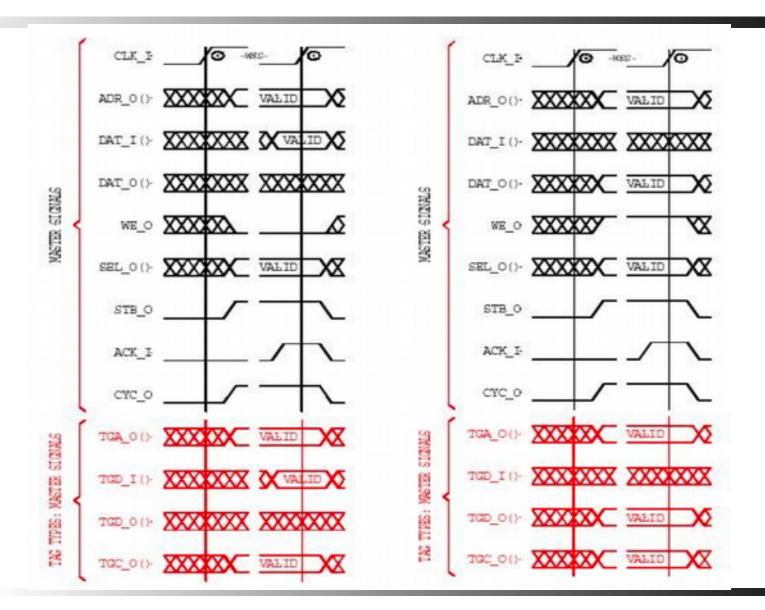

# Wishbone | Read/Write simple

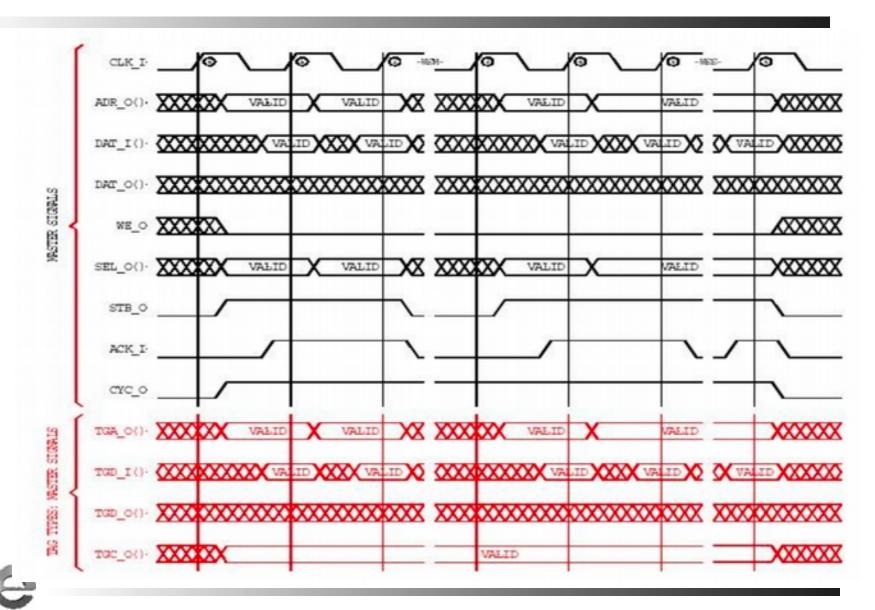

# Wishbone | Read en bloque

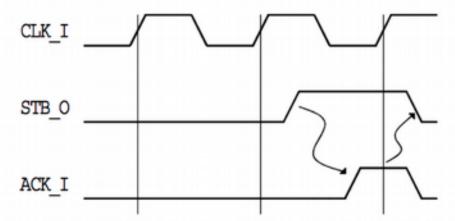

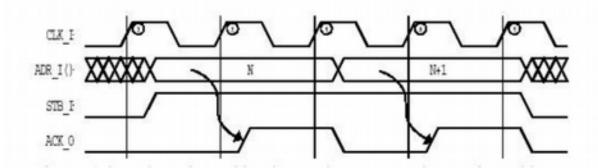

#### Wishbone Clásico

Reconocimiento de ciclos como bucle combinatorio

Figure 4-1 Asynchronous cycle termination path

Figure 3-2. Local bus handshaking protocol.

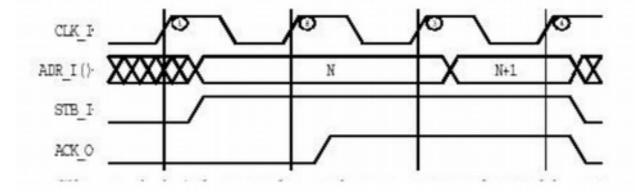

#### Wishbone | Clásico y con ciclos reg.

Cortar el loop para aumentar performance

Reconocimiento de ciclos registrados

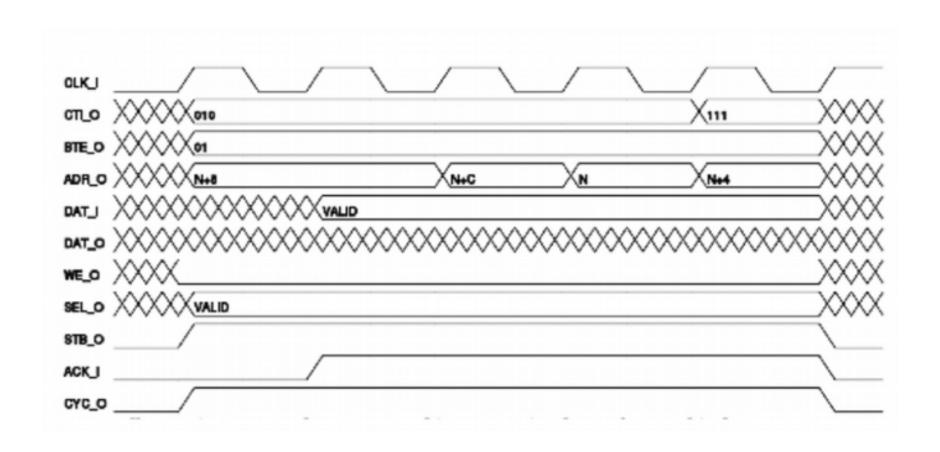

# Wishbone | Tags

| Table 4-2 Cycle Type Identifiers |                              |

|----------------------------------|------------------------------|

| CTI_O(2:0)                       | Description                  |

| '000'                            | Classic cycle.               |

| '001'                            | Constant address burst cycle |

| '010'                            | Incrementing burst cycle     |

| '011'                            | Reserved                     |

| '100'                            | Reserved                     |

| '101                             | Reserved                     |

| '110'                            | Reserved                     |

| '111'                            | End-of-Burst                 |

#### Wishbone | End of cycle

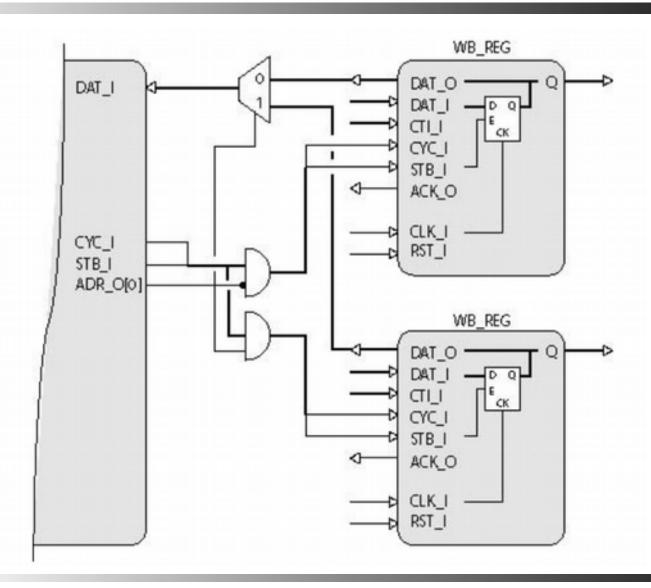

## Wishbone | Ejemplo

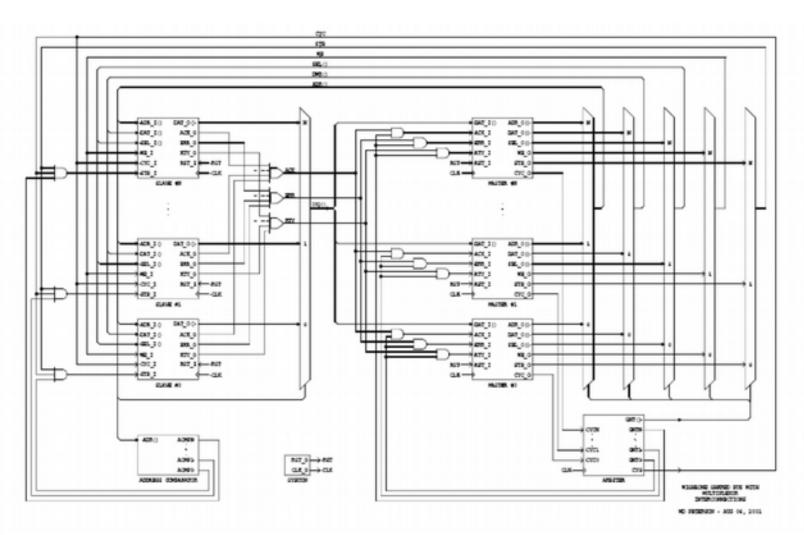

# Wishbone | Multiples esclavos

# Wishbone | Bus compartido

## Wishbone | Registro ciclo registrado

Modificar registro

https://eva.fing.edu.uy/mod/resource/view.php?id=33535

Ref: cap.4 de estándar Wishbone