Serie a Wishbone Master | Diseño de referencia

Serie a Wishbone Master | Diseño de referencia

Requisitos de finalización

El diseño esta pensado para ser utilizado en la placa UP1 de altera (chip EPF10K20RC240-4) y contiene:

El WM Master realiza ciclos Wishbone de Lectura o Escritura simple a la dirección contenida en registro interno.

Protocolo de comunicación y control a través del puerto serie:

Entidades que componen el diseño:

Generics: BAUD_RATE_16x_COUNTER_REFERENCE

vhdl.zip: archivos VHDL: serie2wbm_ref_design.vhd, serie2wbm.vhd, wb_register.vhd y hex27seg.vhd

pin_assignament.txt: lineas a agregar en archivo .QSF para asignar pines rápidamente.

Serie a Wishbone Master | Diseño de referencia

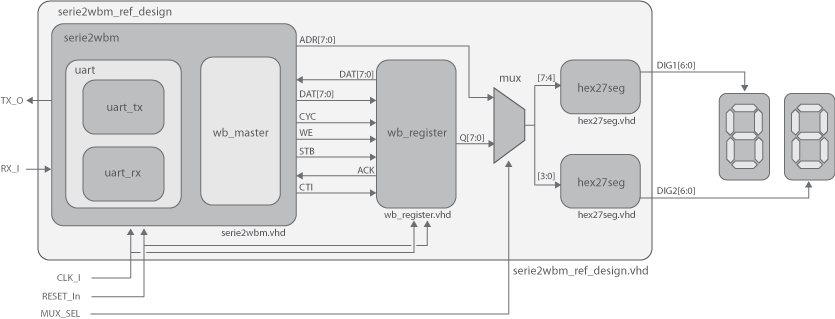

Descripción general

El diseño serie2wbm_ref_design es un diseño de referencia que permite experimentar con diseños con interfaz wishbone y con el diseño serie2wbm.El diseño esta pensado para ser utilizado en la placa UP1 de altera (chip EPF10K20RC240-4) y contiene:

- instancia de bloque serie2wbm

- instancia de bloque wb_register

- multiplexor conectado a instancias de bloques hex27seg y estos a los display 7 seg de forme de visualizar :

- contenido de wb_register (MUX_SEL = 1)

- bus de direcciones de serie2wbm (MUX_SEL = 0)

Detalle de algunas entidades

serie2wbm

Descripcion : Modulo Serie 8N1 a WB MasterEl WM Master realiza ciclos Wishbone de Lectura o Escritura simple a la dirección contenida en registro interno.

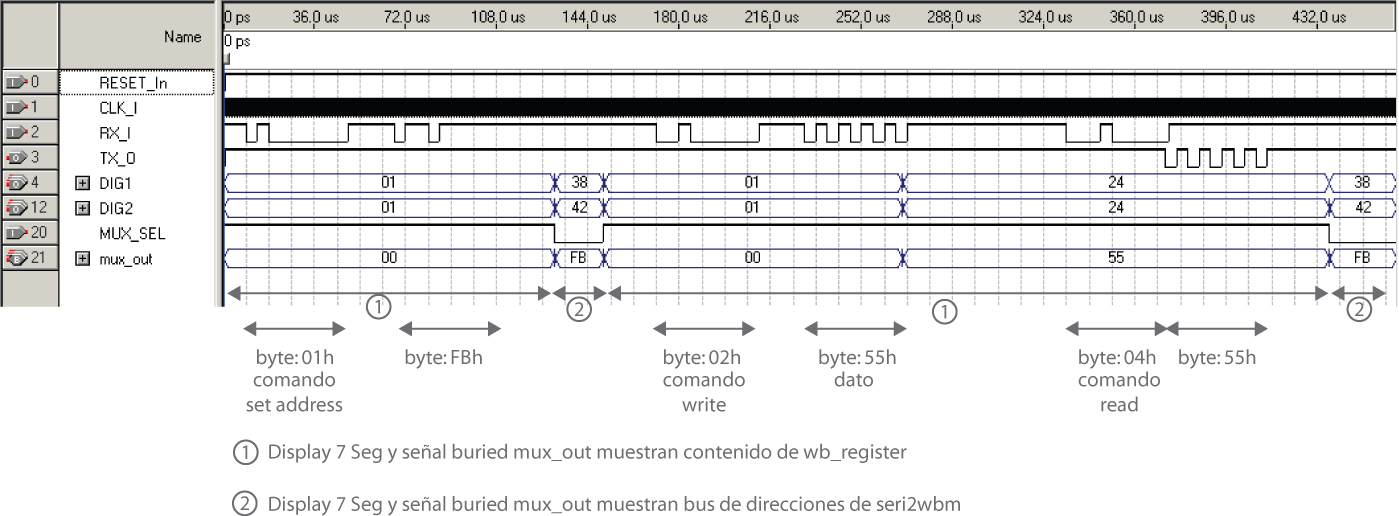

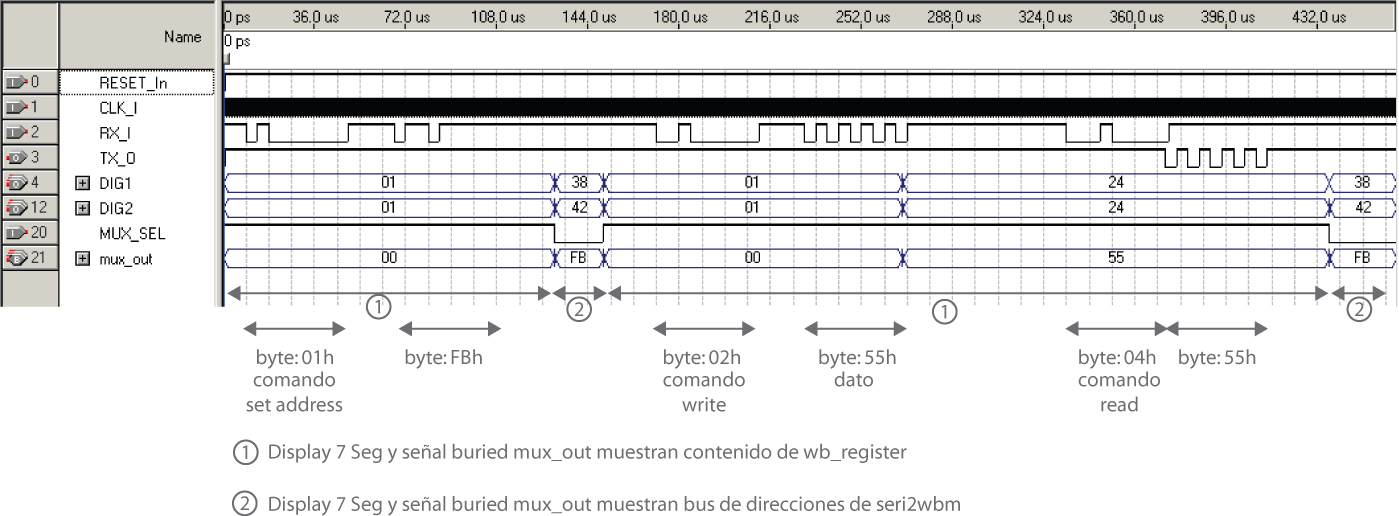

Protocolo de comunicación y control a través del puerto serie:

- Seteo de dirección en registro interno:

- 1. Enviar byte X"01"

- 2. Enviar byte con dirección a cargar en registro

- Ciclo de escritura WB

- 1. Enviar byte X"02"

- 2. Enviar byte con dato a escribir en esclavo WB

- Ciclo de lectura WB

- 1. Enviar byte X"04"

- 2. una vez recibido el dato por parte del maestro WB, es enviado en forma serie

Entidades que componen el diseño:

- serie2wbm

- uart

- uart_rx

- uart_tx

- wb_master

Generics: BAUD_RATE_16x_COUNTER_REFERENCE

- Para Fclk=25.175MHz y 9600bps => BAUD_RATE_16x_COUNTER_REFERENCE = F_CLK_I/(BPS * 15) -1 = 25175000 / (9600 * 15) -1 = 174

Simulación

Para simular el diseño de referencia y diseños que utilicen el bloque serie2wbm se sugiere:- Utilizar un CLK_I con una frecuencia de 10Mhz

- setear el generic BAUD_RATE_16x_COUNTER_REFERENCE en la instancia de serie2wbm en serie2wbm_ref_design en 2

- ajustar tamaño de grilla de simulación a tiempo de bit 4.5us

Archivos disponibles

sim_AddressSet_WriteByte_ReadByte.vwf: Vector para simulaciónvhdl.zip: archivos VHDL: serie2wbm_ref_design.vhd, serie2wbm.vhd, wb_register.vhd y hex27seg.vhd

pin_assignament.txt: lineas a agregar en archivo .QSF para asignar pines rápidamente.