Estimado,

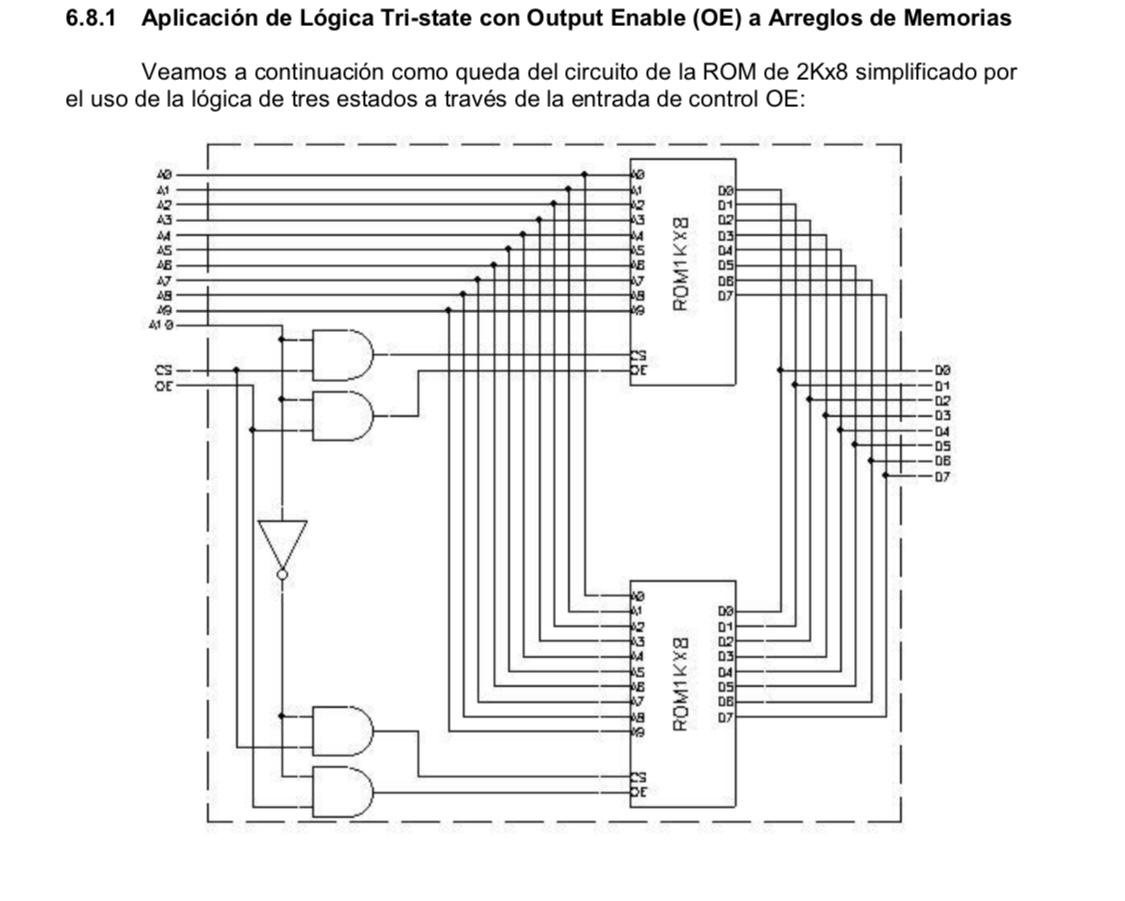

Varias cosas: en primer lugar, lo que ahorra las compuertas AND en la salidas es la entrada OE. La cual permite realizar or cableado entre las salidas de la ROM. De no contar con esta implementación, las salidas de la ROM se deberían multiplexar.

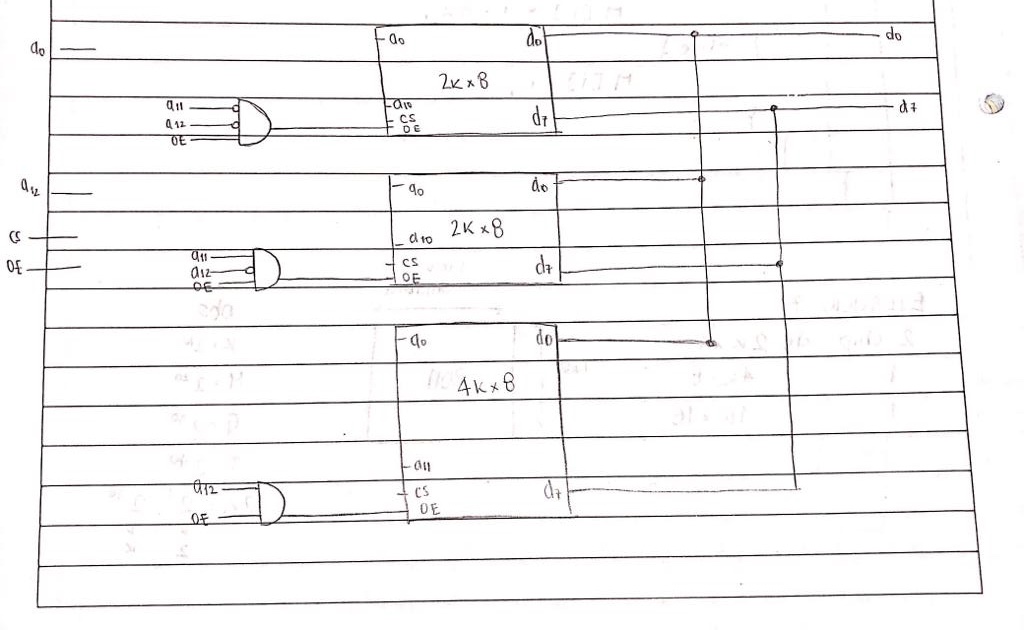

Por otro lado, no hay diferencia a nivel de tabla de verdad entre la solución de uds y la que aparece como solución del parcial. Por la forma como está conectada la entrada OE de las roms, solo una de estas se encontrará activa en cada momento. Es decir, que dos de las roms siempre estarán en 3er estado y la tercera podrá estar en tercer estado o con valor lógico. De este modo, el valor de CS deja de importar para las roms que están en tercer estado (puesto que el OE tiene precedencia sobre el CS), y por tanto no importa si la conexión es como la de su dibujo o la del teórico. Realicen la tabla de verdad y lo van a poder verificar.

Saludos,

Federico

Corrección sobre mi respuesta anterior. Para hacer arreglos de memorias, se debe multiplexar cada salida según los bits de selección de la dirección. Usando CS para hacer la selección, se permite ahorrar los ands en la salida, reduciendo la multiplexación a un conjunto de compuertas OR, y con la selección en OE, se pueden reducir las compueras OR, usando OR cableado.

Lo otro se mantiene, una vez que tenemos seleccionado el OE, como este tiene precedencia sobre el CS, ya no es neesario realizar la selección en CS y esta puede conectarse directamente a la CS de la entrada.

Saludos!

Federico