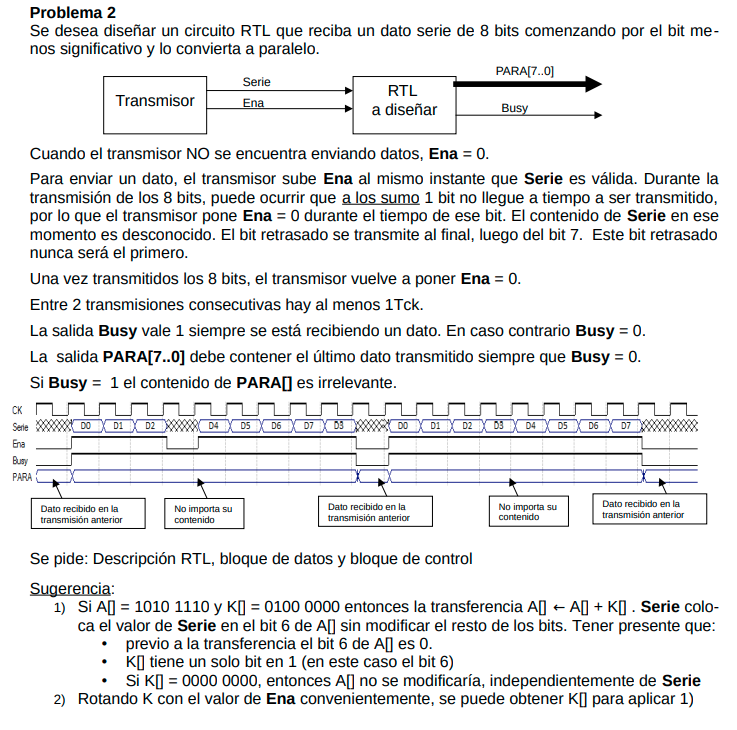

Hola buenas, tengo unas dudas con respecto a la solucion del problema 2. Adjunto el ejercicio, la solucion y luego mis dudas:

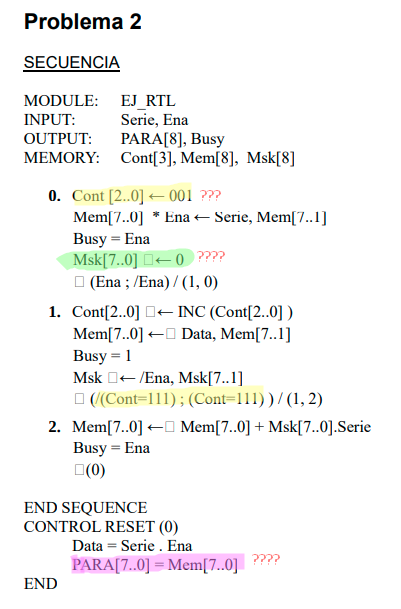

Mi duda es: Cuando en la letra menciona que la salida Para(7..0) debe contener el último dato siempre que Busy=0, y que Para(7..0) es irrelevante si Busy=1, ¿no se deberían hacer transferencias de Mem(7..0) a Para(7..0) solo cuando Busy=0, y no hacer ninguna transferencia cuando Busy=1?

Luego, también me queda la duda de cómo se está usando el cont(3). Ya que, como en el paso 0 arranca con 001, en el paso 1. Mem solo podrá cargar hasta 7 bits de los 8 que son enviados en serie. ¿No debería arrancar cont(3) con 000?

También me llama la atención que no se cargue Mem(7..0) con "0" cuando termina el paso 3. y vuelve al paso 0. , sin embargo, sí se carga Msk(7..0) con 0. Si todas sus celdas se vuelven a cargar con valores nuevos de serie, ¿no debería ser innecesario "resetear" ninguno de los dos?

En respuesta a José Pérez Mereles

Re: Examen Diciembre 2019 Problema 2 RTL

de Juan Pedro Maestrone -

Buenas. Respondo por partes:

1) Justamente que diga que Para[7..0] es irrelevante cuando Busy=1 implica que no importa que hagas transferencias cuando Busy=1. Por eso mismo la conexión Para[7..0] = Mem[7..0] se pone luego del end sequence, ya que minimiza la lógica final (si se pusiera solo en los pasos en los que Busy=0 habría que agregar compuertas AND con esos pasos, y una compuerta OR si se pone en más de 1 paso). De todas formas si lo pusieras solo en los pasos en los que Busy=0 no habría problema, lo que sí además de lo anterior estarías imponiendo Para[7..0]=0 en los pasos en donde no indiques el valor de dicha salida (por convención de salidas en RTL).

2) Tienes razón, es un typo de la solución; debería ser cont[2..0] <-- 0.

3) También tienes razón, no es necesario poner Msk[7..0] <-- 0 ya que luego sobreescribes los 8 bits.

Saludos,

Juan Pedro.

1) Justamente que diga que Para[7..0] es irrelevante cuando Busy=1 implica que no importa que hagas transferencias cuando Busy=1. Por eso mismo la conexión Para[7..0] = Mem[7..0] se pone luego del end sequence, ya que minimiza la lógica final (si se pusiera solo en los pasos en los que Busy=0 habría que agregar compuertas AND con esos pasos, y una compuerta OR si se pone en más de 1 paso). De todas formas si lo pusieras solo en los pasos en los que Busy=0 no habría problema, lo que sí además de lo anterior estarías imponiendo Para[7..0]=0 en los pasos en donde no indiques el valor de dicha salida (por convención de salidas en RTL).

2) Tienes razón, es un typo de la solución; debería ser cont[2..0] <-- 0.

3) También tienes razón, no es necesario poner Msk[7..0] <-- 0 ya que luego sobreescribes los 8 bits.

Saludos,

Juan Pedro.

En respuesta a Juan Pedro Maestrone

Re: Examen Diciembre 2019 Problema 2 RTL

de José Pérez Mereles -

Muchas gracias por las respuestas !!