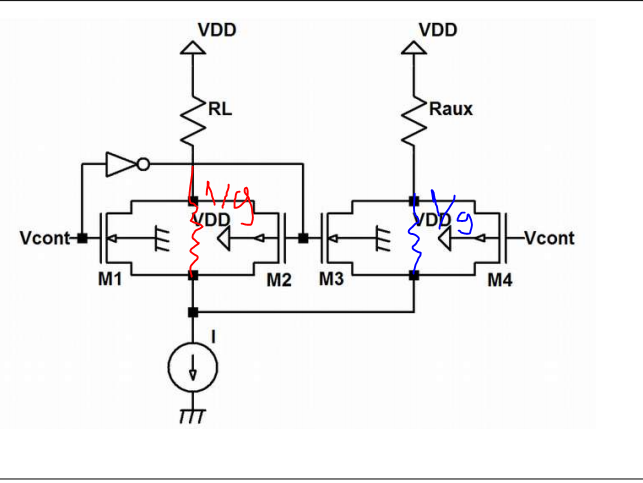

Buenass, haciendo este parcial me surgió una duda en el ejercicio 2. Porque creo al resolver toma como que la corriente que pasa por M1 y M2 es la de la fuente de corriente, cuando en verdad hay un nudo y se forma un paralelo entre la rama de M1 y M2 con la rama de M3 y M3. No se si estoy siendo clara. O sea yo plantee una equivalencia como la del dibujo:

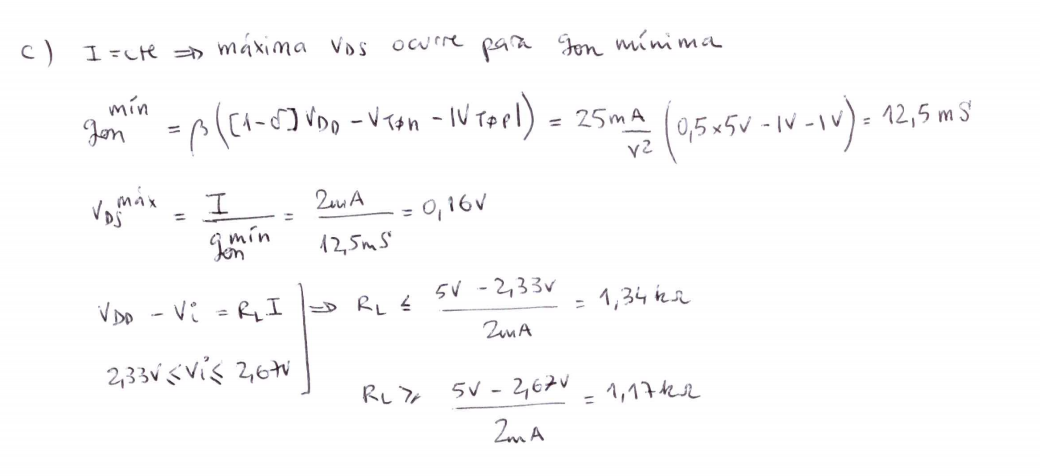

Y entonces con el mismo razonamiento de la solución podes hallar Vi que vendría a ser el voltaje en la entrada de la resistencia roja. Pero después la solución usa directamente la corriente I para resolver la rama roja, cuando en verdad hay un nudo y la corriente por esa rama no va a ser I, sino que va a depender del paralelo que se forma ahí. Gracias.

Adjunto la solución también

Edición 5 min después cuando me di cuenta, es porque los vdd y tierras de la otra llave estan invertidas no? Entonces no me cambia nada.