Buenas, tengo una duda con este ejercicio, como por cada linea de cache hay 2^3 bytes y los elementos de cada matriz son contiguos, si voy a buscar a cache primero se produce un miss y luego 2^3-1 hits por el tamaño de la linea, y esto pasa cuatro veces porque cada matriz tiene 2^5 bytes, luego CANT_MATRICES veces.

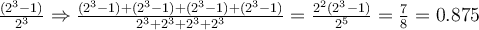

Entonces me queda que el hit rate es  , estaría mal?

, estaría mal?

Se supone que siempre que se va a buscar a cache se trae un byte no una palabra? como sería el acceso a la caché al ejecutar la siguiente instruccion: ADD AX,ES:[MATRICES+SI+BX]?

Primero se busca en caché la parte baja y luego la alta en dos accesos a caché distintos o como sería?

Saludos