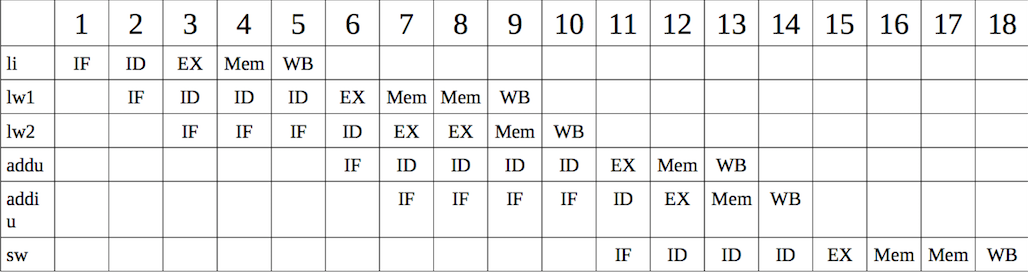

Hola, no se porque el fetch es retrasado en la instruccion lw2, entiendo que no se pueda hacer a la misma vez que un MEM por temas acceso a memoria, pero no se pq no lo hace a la misma vez que EX.

Saludos.

Hola, no se porque el fetch es retrasado en la instruccion lw2, entiendo que no se pueda hacer a la misma vez que un MEM por temas acceso a memoria, pero no se pq no lo hace a la misma vez que EX.

Saludos.

Estimado:

Algunas aclaraciones:

1) En la letra está aclarado que se trata de memorias diferentes, por lo cual no se producirían hazards estructurales en el acceso a memoria (es decir, se puede realizar el fetch en el mismo ciclo que se realiza un load o store).

2) La detención del ciclo 4 es por la dependencia RaW entre la primera y segunda instrucción. LW1 debe esperar, y por tanto LW2 también pues sinó sobreescribiría los valores de la instrucción LW1.

Cualquier otra duda preguntá! :)

Saludos,

Federico

Pareciera que hubiera un stall de más en la tercera etiqueta de ID de lw1. ¿Por qué pasa eso? ¿No se puede forwardear el inmediato de alguna manera a lw1?

Estimado:

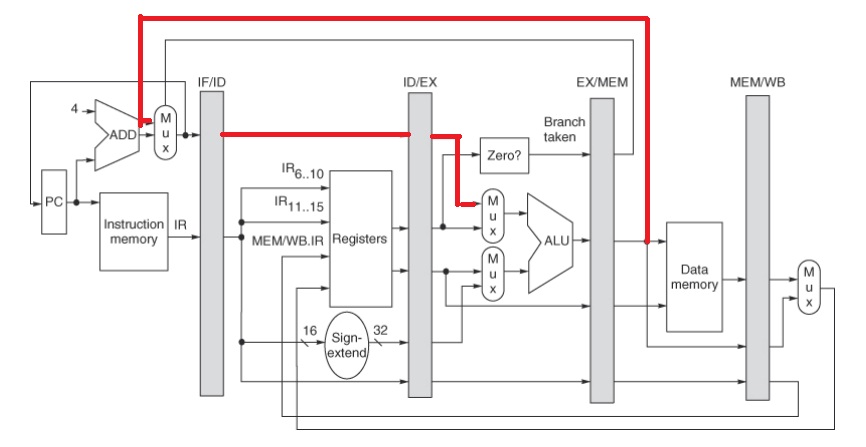

Parte del ejercicio es notar que no hay ningún mecanismo de forwarding implementado (ver dibujo). Si hubiera forwarding implementado, se podrían eliminar los tres ciclos de stall.

Saludos,

Federico

Entiendo. No estoy familiarizado con cómo sería el dibujo si hubiera forwarding. ¿Hay algún ejemplo en la bibliografía o en las diapositivas?

Supongo que serían necesarias las líneas que unen los registros de pipeline con las unidades que tienen inmediatamente detrás, que se ven en los diagramas de pipeline que tienen las unidades del camino de datos dibujadas. Aún así no es muy ilustrativo esto, creo.

Estimado:

Sí, en la bibliografía:

Esto es tomado del libro del curso.

Entiendo que digas que no es muy ilustrativo, pero el problema es que practicamente cualquier diagrama de pipeline tiene sentido para un hardware y configuración de forwarding en particular, y dado eso, la mejor convención que se puede dar es mostrar un cierto hardware. Además, este en particular mantenía prácticamente todas las reglas del pipeline presentado en teórico, por lo que no había una gran cuota de deducción necesaria para realizar el ejercicio.

Saludos,

Federico

Justo acababa de ver esa imagen en el libro y venía a publicarla. Está en la página A-37, por si alguien la quiere buscar.

Gracias. Saludos.

ese forwarding queda mucho mas claro.

Pero, la linea que marque de rojo en el dibujo ¿que hace?. Yo lo habia interpretado como un forwarding de la salida del EX a la entrada del ID

Estimado:

Negativo, es el flujo que sigue el PC durante un salto, si es que este se toma. Si la instrucción a ejecutar es un branch o un jump, el PC será elegido como entrada de la ALU, y su resultado será elegido en lugar de PC + 4 para cambiar el valor del PC.

Saludos!