Hola tengo una duda: en qué impacta que el Ron de la llave cmos se comporte así? No capté esa parte, gracias. Supongo lo hace más eficiente que un nmos o un pmos pero no veo cómo

Hola tengo una duda: en qué impacta que el Ron de la llave cmos se comporte así? No capté esa parte, gracias. Supongo lo hace más eficiente que un nmos o un pmos pero no veo cómo

Hola,

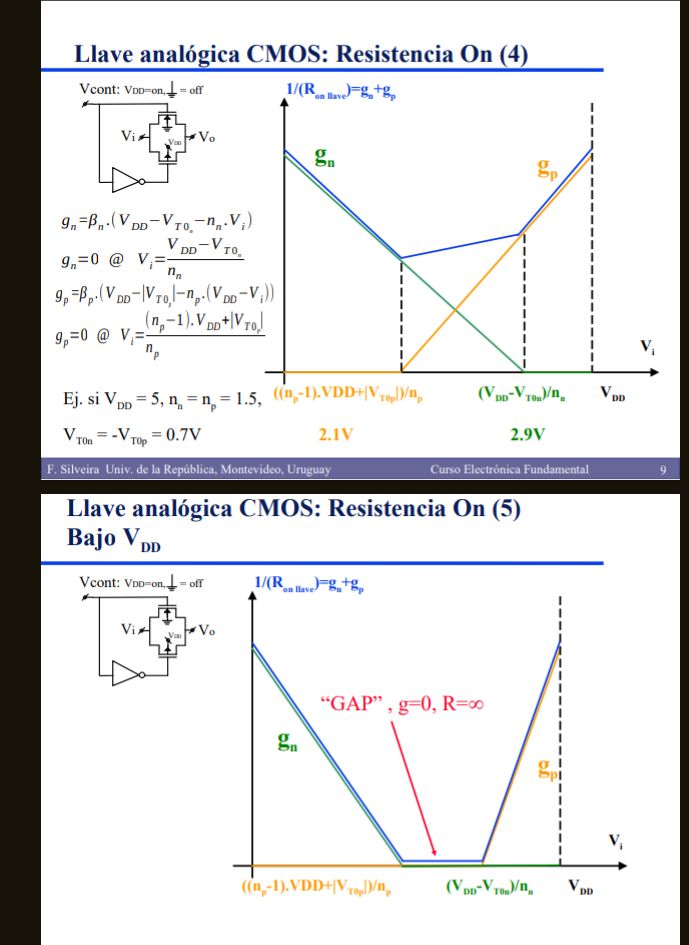

En la primera de las diapositivas vemos la evolución de la conductancia de la llave (inverso de la resistencia Ron) en función de la tensión que estamos conectando Vi.

En verde está el caso en que usáramos solo un nMOS y en naranja si usáramos solo un pMOS. En estos dos casos se ve que hay valores de Vi en los cuáles la conductancia da 0 (es decir la resistencia es infinita) y por tanto la llave no conduce, no conecta sus dos extremos como queremos. O sea usando solo un nMOS o solo un pMOS no podemos tener una llave que funcione para cualquier Vi entre 0 y VDD.

En azul está el caso en que tenemos los dos en paralelo y allí se ve que la conductancia es siempre mayor a 0 o sea la llave conduce para todos los Vi entre 0 y VDD.

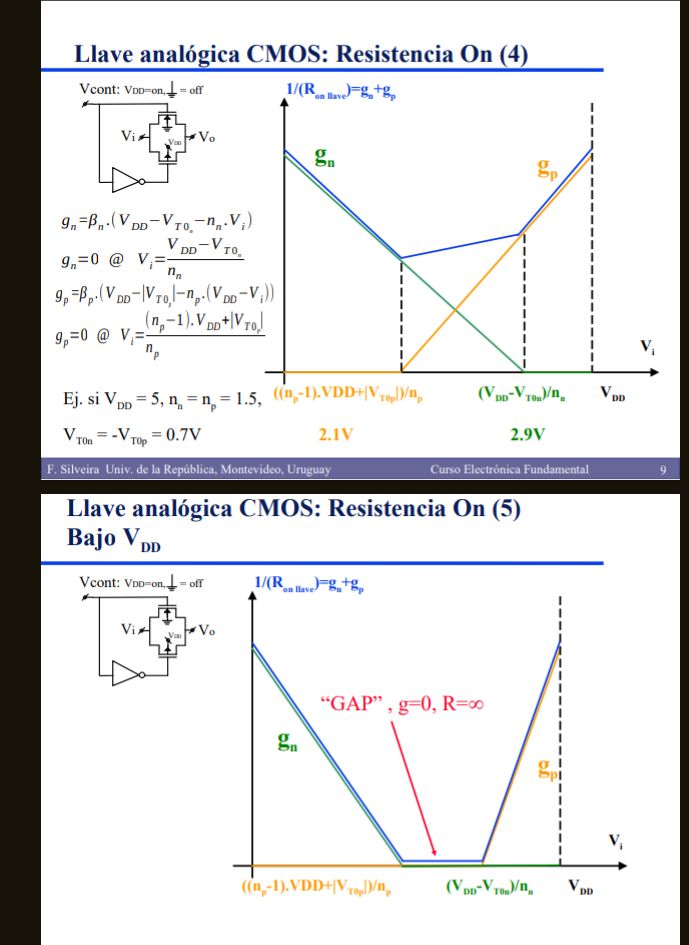

Esto último es cierto siempre y cuando la tensión de alimentación VDD no sea demasiado baja. Si VDD baja mucho ocurre lo que se ve en la segunda diapositiva, que aún con la llave con nMOS y pMOS en paralelo hay una zona cercana a VDD/2 en que ninguno de los dos transistores conduce.

Saludos,

Fernando

Buenas tardes, viendo la discusión me surgió una duda. En teórico vimos que el nMOS que no era bueno para cargar una capacidad cuando el voltaje en la entrada  tomaba el valor del voltaje en el gate

tomaba el valor del voltaje en el gate  , porque en un instante se cortaba. La duda es, si en

, porque en un instante se cortaba. La duda es, si en  estamos trabajando con voltajes tales que el máximo valor es bastante mas chico que la tensión

estamos trabajando con voltajes tales que el máximo valor es bastante mas chico que la tensión  entonces no había necesidad de usar la llave analogica, no? Podría cargar y descargar esa capacitancia sin problemas. Creo que además el transistor nunca funcionaría en saturación.

entonces no había necesidad de usar la llave analogica, no? Podría cargar y descargar esa capacitancia sin problemas. Creo que además el transistor nunca funcionaría en saturación.

Saludos,

Nicolás.

Hola,

Lo que ocurre es que si querés manejar voltajes entre 0 y VDD, como al transistor para encenderlo también le ponés VDD en VGB, está queriendo llegar hasta el VP y por encima del VP (que es menor a VDD).

Si se tratara de un caso particular en que la llave solo tiene que conectar tensiones chicas, menores a VP, si, alcanzaría con usar solamente un transistor nMOS.

Saludos,

Fernando