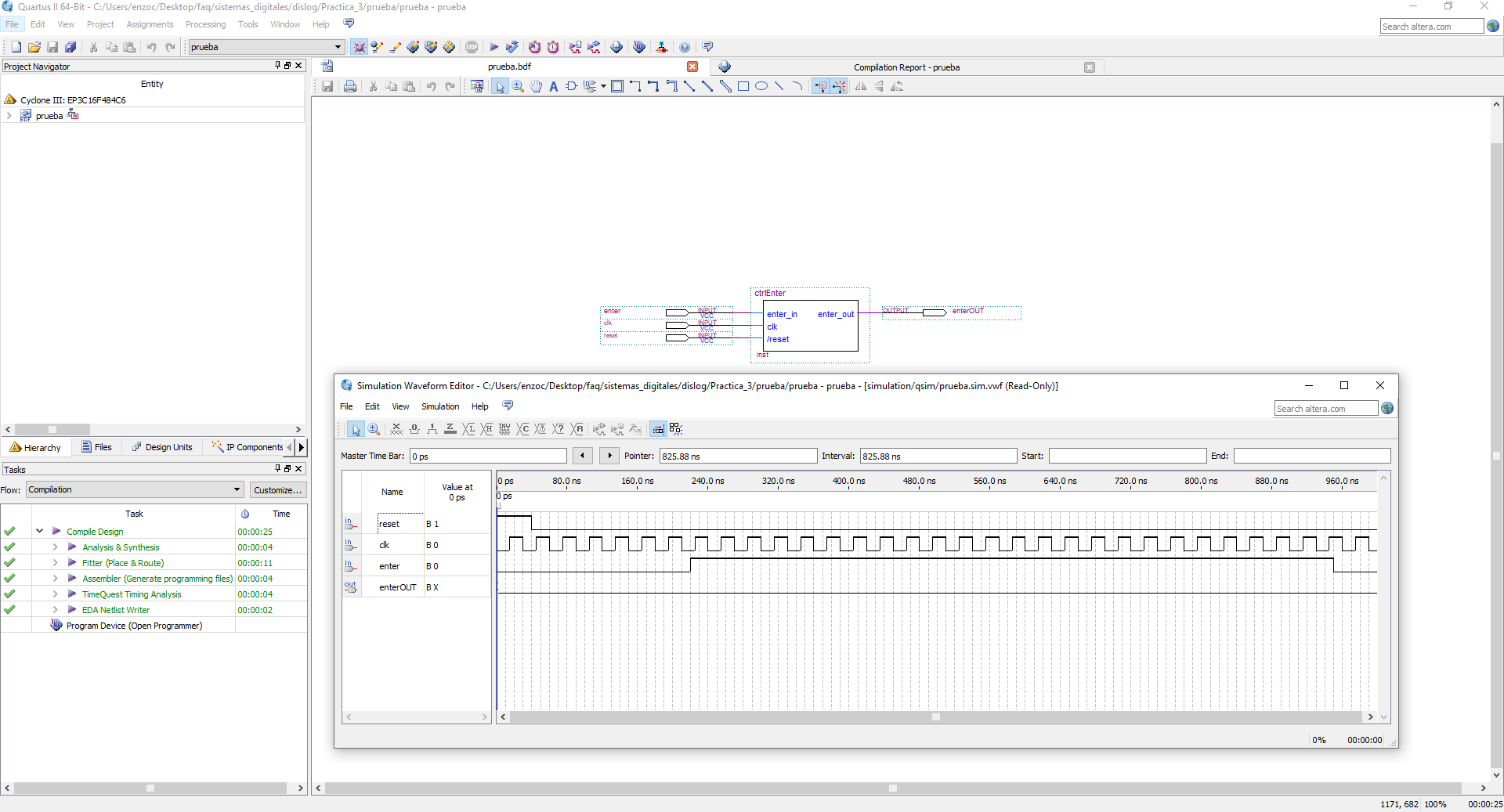

Estamos teniendo un problema con el bloque "ctrlEnter" que nos dan para realizar el masterMind. Cuando simulamos solamente este bloque la salida siempre da 0 constantemente. Probamos simular de varias formas, incluso sacando los divisores de frecuencia, pero la salida siempre es 0. Cuando simulamos la parte a nos dan bien las cosas, pero al momento de pasarlo a la placa con el circuito de prueba, cuando apretamos el botón "enter" no pasa nada.