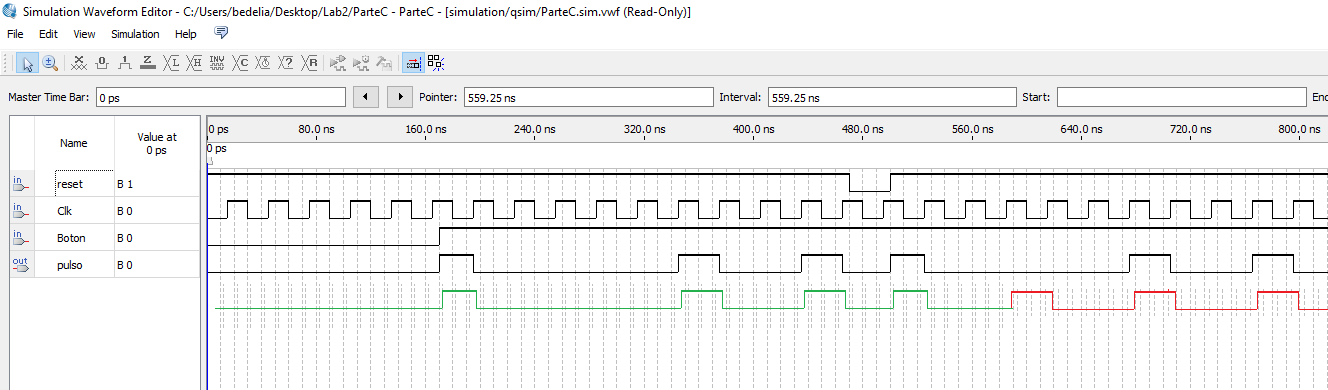

Si dejamos reset en 1 todo el tiempo el circuito funciona normal.

Cuando bajamos reset a 0, en la simulación se muestra que la salida se va a 0 y es independiente del valor de botón. Luego, al volver a activar reset, el circuito funciona normalmente. De ahí deducimos que en la simulación, accionar reset lleva al circuito al estado inicial.

En la placa No ocurre esto. Cuando dejamos botón activo por más de 5 flancos de reloj, la salida empieza a oscilar como se espera. Pero al accionar reset la salida va a 0, y cuando se vuelve reset a 1, la salida sigue oscilando como si nunca se hubiera apagado.

En la imagen se ve mejor lo que nos está ocurriendo. La linea verde es hasta donde la placa se comportó igual que en la simulación. La linea roja es la discrepancia. ¿Es normal que la placa de una salida distinta a la de la simulación?