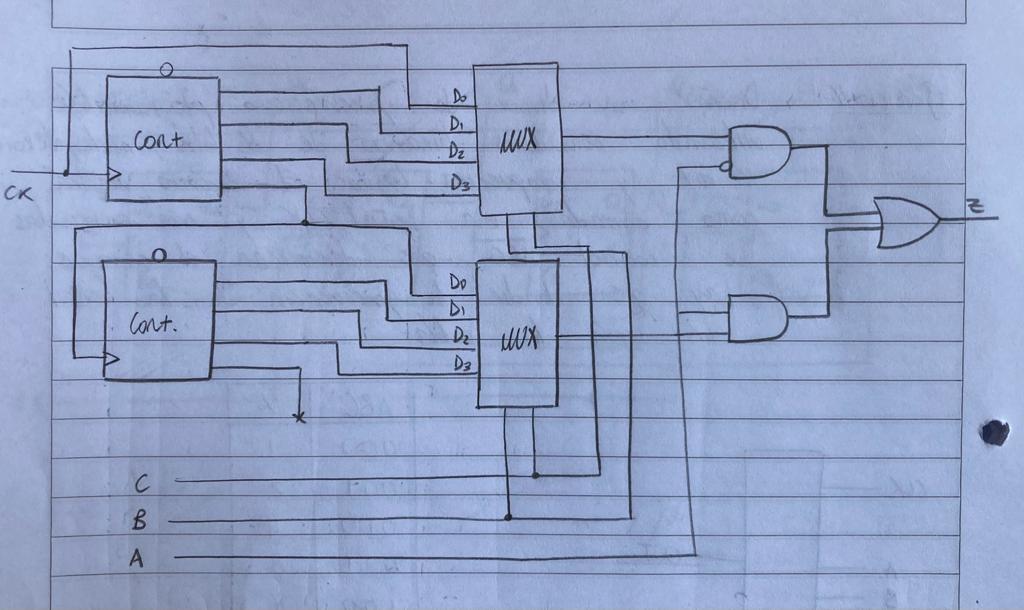

Buenas tardes, estaba haciendo estos ejercicios y me surgieron algunas dudas. Con respecto al ejercicio 4 creo que llegue a una solución que parece coherente; poner dos contadores de cuatro bits seguidos donde cada salida es la frecuencia dividida. El 'bit mas significativo" del primer contador se conecta al reloj del segundo contador. Luego con dos multiplexores cuatro a uno controlo que frecuencia elijo como salida con las entradas 'C' y 'B' y finalmente 'A' elige entre las dos salidas de lo MUX. Esto funciona? Dejo foto.

Con respecto al ejercicio 6, no comprendo totalmente que es lo que se pide. Se dice que debe proporcionar un retardo de dos o tres periodos de reloj. Yo entiendo que la salida debe ser igual a la entrada desfasada en un cantidad de periodos según entrada de control. Al leer la letra, si bien pide un diagrama de estados, se me ocurrió usar un registro de desplazamiento de cuatro bits y con un multiplexor seleccionar entre la salida del ultimo flip-flop o del penúltimo flip-flop según la entrada r que controla el MUX. Ahora, yo no se si la entrada esta sincronizada con el reloj o no, entonces si cambia muchas veces entre flanco y flanco, todo eso me lo pierdo al ponerlo en la salida (creo que pondría el ultimo valor estable de la entrada antes de que llegue el pulso). No se si esto esta bien, ni si es la forma en la que hay que encararlo, así que toda ayuda es bienvenida.

Saludos,

Nicolas.

Imagen del ej4.