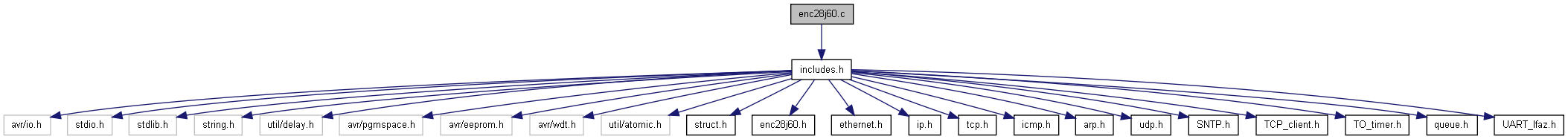

Referencia del Archivo enc28j60.c

Implementacion del driver ENC28J60.. Más...

#include "includes.h"

Funciones | |

| BYTE | enc28j60ReadOp (BYTE op, BYTE address) |

| Implementa operaciones del tipo lectura Enmascara OPCODE y address para generar el comando: O0 O1 O2 A0 A1 A2 A3 A4 espera a que llegue el dato y lo devuelve. | |

| void | enc28j60WriteOp (BYTE op, BYTE address, BYTE data) |

| Implementa operaciones del tipo escritura Enmascara OPCODE y address para generar el comando: O0 O1 O2 A0 A1 A2 A3 A4 Escribe el dato. | |

| void | enc28j60SetBank (BYTE address) |

| Setea el banco con el que se esta trabajando. | |

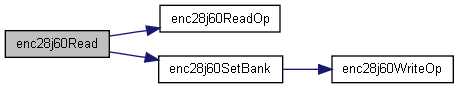

| BYTE | enc28j60Read (BYTE address) |

| Implementa lectura de un registro setea el banco usando la primer parte de la direccion llama a ReadOp usando OPCODE de lectura de registro y address. | |

| void | enc28j60Write (BYTE address, BYTE data) |

| Implementa escritura de un registro setea el banco usando la primer parte de la direccion llama a WriteOp usando OPCODE de escritura de registro y address. | |

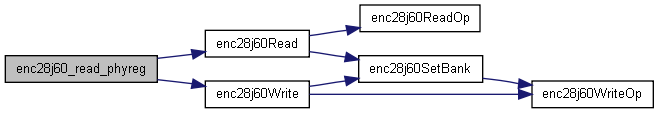

| WORD | enc28j60_read_phyreg (BYTE address) |

| Implementa lectura de un registro del tipo PHY ver datasheet por diferencias con lectura comun. | |

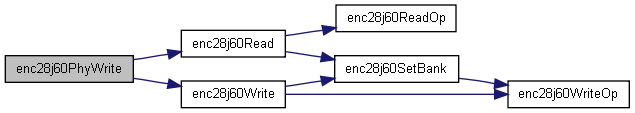

| void | enc28j60PhyWrite (BYTE address, WORD_BYTES data) |

| Implementa escritura de un registro PHY ver datasheet por diferencias con lectura comun. | |

| void | enc28j60_init (BYTE *avr_mac) |

| Inicializa el puerto SPI y el chip ENC28J60 La inicializacion se hace en base a las recomendaciones del datasheet inicializa buffers Tx y Rx inicializa capa MAC inicializa capa PHY. | |

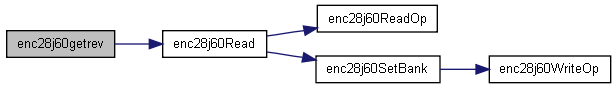

| BYTE | enc28j60getrev (void) |

| lee "Silicon Revision Level" (no es muy necesario) | |

| void | enc28j60_packet_send (BYTE *buffer, WORD length) |

| Envia un paquete Escribe un bloque de memoria en el buffer Tx del ENC y lo envia a la red. Agrega el byte de control necesario para el ENC previo a cada paquete a ser transmitido. El ENC se encarga de agregar el preambulo, CRC y padding necesarios. | |

| WORD | enc28j60_packet_receive (BYTE *rxtx_buffer, WORD max_length) |

| Lee un paquete que llega al ENC Escribe el paquete recibido a RAM. Devuelve el largo del paquete. | |

Variables | |

| static BYTE | Enc28j60Bank |

| static WORD_BYTES | next_packet_ptr |

Descripción detallada

Implementacion del driver ENC28J60..

Implementa los metodos de envio/recibo de paquetes y de escritura/lectura de los registros de control del ENC28J60.

Documentación de las funciones

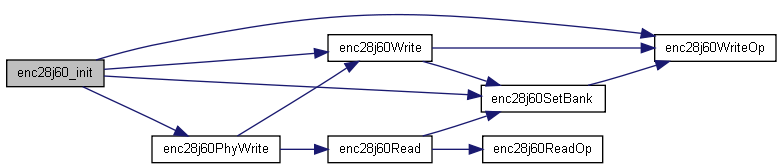

| void enc28j60_init | ( | BYTE * | avr_mac | ) |

Inicializa el puerto SPI y el chip ENC28J60

La inicializacion se hace en base a las recomendaciones del datasheet

inicializa buffers Tx y Rx

inicializa capa MAC

inicializa capa PHY.

- Parámetros:

-

avr_mac puntero a la direccion MAC

enable PD3, reset as output

INICIALIZACION DE ETHERNET

puntero al siguiente paquete= dir rx inicial

ERXST= RXSTART_INIT (ETHERNET RECEIVE BUFFER START POINTER)

ERXRDPT= RXSTART_INIT (ETHERNET RECEIVE BUFFER READ POINTER)

ERXND= RXSTOP_INIT (ETHERNET RECEIVE BUFFER END POINTER)

ETXST= TXSTART_INIT posicion del paquete a trasmitir (inicial)

ETXND= TXSTOP_INIT

INICIALIZACION DE LA MAC

MARXEN: ENEBLE MAC TO RECEIVE FRAMES

TXPAUS Y RXPAUS: SE SETEAN SI USO FULL DUPLEX XA CONTROL DE FLUJO

bring MAC out of reset

enable automatic padding to 60bytes and CRC operations

LA MAC ESPERA INDEFINIDAMENTE A QUE SE LIBERE EL MEDIO PARA TRANSMITIR

SE ANULA EL TIMEOUT PARA TRANSMISION

Set non-back-to-back inter-packet gap to 9.6us. The back-to-back inter-packet gap (MABBIPG) is set by MACSetDuplex() which is called later.

Set the maximum packet size which the controller will accept.

Do not send packets longer than MAX_FRAMELEN:

write MAC address

NOTE: MAC address in ENC28J60 is byte-backward ENC28J60 is big-endian avr gcc is little-endian

no loopback of transmitted frames

do bank 1 stuff, packet filter:

For broadcast packets we allow only ARP packtets

All other packets should be unicast only for our mac (MAADR)

The pattern to match on is therefore

Type ETH.DST

ARP BROADCAST

06 08 -- ff ff ff ff ff ff -> ip checksum for theses bytes=f7f9

in binary these poitions are:11 0000 0011 1111

This is hex 303F->EPMM0=0x3f,EPMM1=0x30

PMEN=PATTERN MATCH

CRCEN = POST FILTER CRC ENABLE

UCEN= UNICAST ENABLE

EPMM0= 0x3f,EPMM1= 0x30

SETEA DONDE ESTA EL PATRON ADENTRO DEL MENSAJE

EPMCSL= 0xf9, EPMCSH= 0xf7

PATERN MATCH CHECKSUM

set inter-frame gap (back-to-back)

switch to bank 0

enable interrutps

enable packet reception

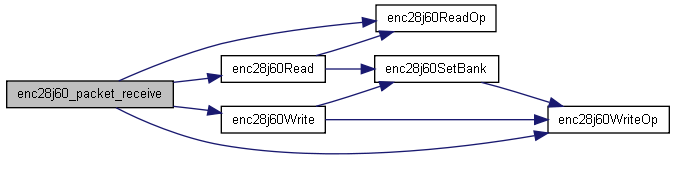

Lee un paquete que llega al ENC

Escribe el paquete recibido a RAM.

Devuelve el largo del paquete.

- Parámetros:

-

rxtx_buffer espacio de memoria donde se colocaran los datos recibidos max_length largo maximo de datos a leer

check if a packet has been received and buffered

Set the read pointer to the start of the received packet

read the next packet pointer

read the packet length (see datasheet page 43)

read the receive status (see datasheet page 43)

check CRC and symbol errors (see datasheet page 44, table 7-3): The ERXFCON.CRCEN is set by default. Normally we should not need to check this.

read data from rx buffer and save to rxtx_buffer

Move the RX read pointer to the start of the next received packet

decrement the packet counter indicate we are done with this packet

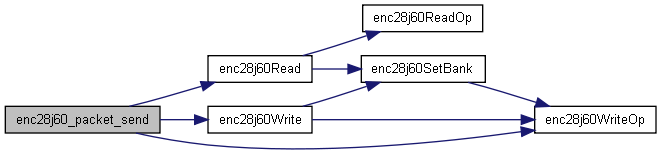

Envia un paquete

Escribe un bloque de memoria en el buffer Tx del ENC y lo envia a la red.

Agrega el byte de control necesario para el ENC previo a cada paquete a ser transmitido.

El ENC se encarga de agregar el preambulo, CRC y padding necesarios.

- Parámetros:

-

buffer espacio de memoria donde estan los datos a enviar length largo de datos

Set the write pointer to start of transmit buffer area

Set the TXND pointer to correspond to the packet size given

write per-packet control byte (0x00 means use macon3 settings)

issue write command

write data

send the contents of the transmit buffer onto the network

Reset the transmit logic problem. See Rev. B4 Silicon Errata point 12.

Implementa lectura de un registro del tipo PHY ver datasheet por diferencias con lectura comun.

- Parámetros:

-

address un registro

set the PHY register address

Loop to wait until the PHY register has been read through the MII This requires 10.24us

Stop reading

Obtain results and return

| BYTE enc28j60getrev | ( | void | ) |

lee "Silicon Revision Level" (no es muy necesario)

| void enc28j60PhyWrite | ( | BYTE | address, | |

| WORD_BYTES | data | |||

| ) |

Implementa escritura de un registro PHY

ver datasheet por diferencias con lectura comun.

- Parámetros:

-

address un registro data dato a escribir

set the PHY register address

write the PHY data

wait until the PHY write completes

Implementa lectura de un registro

setea el banco usando la primer parte de la direccion

llama a ReadOp usando OPCODE de lectura de registro y address.

- Parámetros:

-

address un registro

selecciona banco a leer.

lee utilizando ReadOp

Implementa operaciones del tipo lectura

Enmascara OPCODE y address para generar el comando:

O0 O1 O2 A0 A1 A2 A3 A4

espera a que llegue el dato y lo devuelve.

- Parámetros:

-

op un opcode. address un registro

pongo activo el CS indicando inicio de Tx

envio comando de lectura

espero que el comando sea enviado

escribir el SPDR hace q se inicie una transmision de 1 byte

espero a que llegue el dato que queda guardado en SPDR

si necesito doble lectura(la anterior fue dummy y debo hacer otra)(for mac and mii, see datasheet page 29)

| void enc28j60SetBank | ( | BYTE | address | ) |

Setea el banco con el que se esta trabajando.

- Parámetros:

-

address nombre del banco

LA MEMORIA SE DIVIDE EN 4 BANCOS SELECCIONABLES POR MEDIO DE BSEL0,1 (VER PAG 14)

setea el banco solo si es diferente del actual

LIMPIA LOS 2 MEDIANTE AND CON 11111100

HACE UN OR ENMASCARADO: 000000XX

GUARDA REGISTRO DE EN Q BANCO ESTOY

Implementa escritura de un registro

setea el banco usando la primer parte de la direccion

llama a WriteOp usando OPCODE de escritura de registro y address.

- Parámetros:

-

address un registro data dato a escribir

selecciona el banco en q va a escribir

escribe el registro utilizando WriteOp

Implementa operaciones del tipo escritura

Enmascara OPCODE y address para generar el comando:

O0 O1 O2 A0 A1 A2 A3 A4

Escribe el dato.

EJECUCION DE COMANDOS DE ESCRITURA

LOS 7 COMANDOS SON UN OPCODE DE 3 BITS + UN ARGUMENTO DE 5 BITS(ADDRESS) Y EL SIGUIENTE BYTE ES EL DATO

OP ES EL COMANDO: (VER INSTRUCTION SET)

ADDRESS INDICA EL ARGUMENTO

DATA ES EL DATO Q SE ESCRIBE

- Parámetros:

-

op un opcode. address un registro data el dato a escribir

indica comando escribir y a que direccion

espera a que se active flag de interrupcion de spi (o sea que haya llegado el comando)

escribe el dato en SPDR (es SPI I/O data register)

Documentación de las variables

BYTE Enc28j60Bank [static] |

WORD_BYTES next_packet_ptr [static] |

1.5.6

1.5.6