### Estudio de tiempos hardware

- Requerimientos de tiempo en uP y memorias.

- Tiempos de setup, hold y anchos de pulso.

- Para todos los chips.

- Para todos los ciclos M.

- Varios grados de libertad:

- fck, modelo uP, modelo memoria, inserción de Tw.

- Performance vs. Consumo vs. Costo

- Diferentes análisis según restricciones

- uP y fck fijo, 0 Tw => elegir la memoria

- uP, fck fijo y chip memoria fijos => cuántos Tw necesito

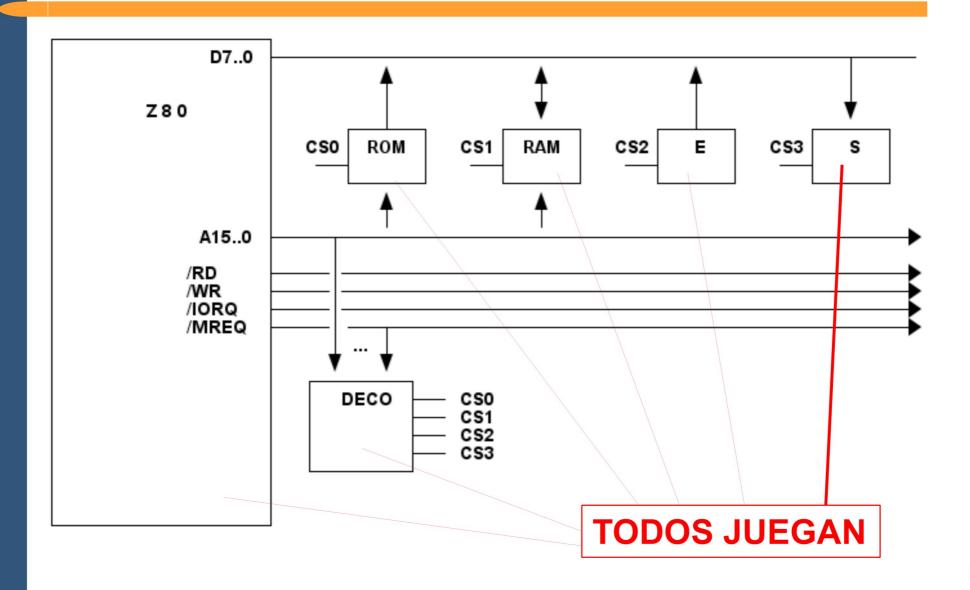

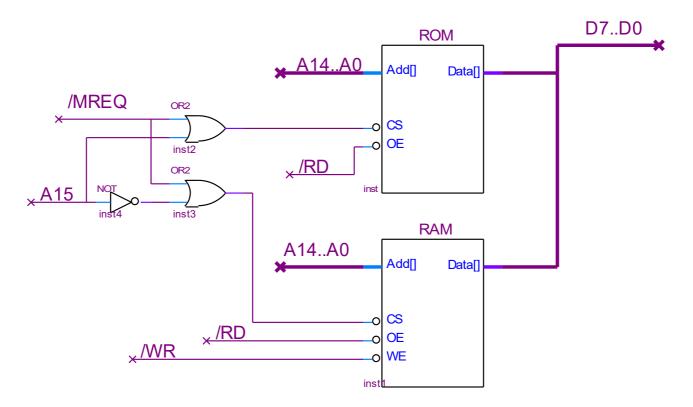

### Sistema

## Requerimientos y Retardos

|    | Symbol      | Parameter                       | Z84C0004 |     | Z84C0006 |     | Z84C0008 |     | Z84C0010 |     | Z84C0020[1] |     | Unit | A1-4 |

|----|-------------|---------------------------------|----------|-----|----------|-----|----------|-----|----------|-----|-------------|-----|------|------|

| No |             |                                 |          | Max |          | Max |          | Max |          | Max |             | Max | Onk  | NOTE |

| 1  | TcC         | Clock Cycle time                | 250*     | DC  | 162*     | DC  | 125*     | DC  | 100*     | DC  | 50°         | DC  | nS   |      |

| 2  | TwCh        | Clock Pulse width (high)        | 110      | DC  | 65       | DC  | 55       | DC  | 40       | DC  | 20          | DC  | nS   |      |

| 3  | TwCi        | Clock Pulse width (low)         | 110      | DC  | 65       | DC  | 55       | DC  | 40       | DC  | 20          | DC  | nS   |      |

| 4  | TfC         | Clock Fall time                 |          | 30  |          | 20  |          | 10  | 100      | 10  |             | 10  | nS   |      |

| 5  | TrC         | Clock Rise time                 |          | 30  |          | 20  |          | 10  |          | 10  |             | 10  | nS   |      |

| 6  | TdCr(A)     | Address vaild from Clock Rise   | 1        | 110 |          | 90  | - 1000   | 80  | _        | 65  |             | 57  | nS   | [2]  |

| 7  | TdA(MREQf)  | Address valid to /MREQ Fall     | 65*      |     | 35*      |     | 20*      |     | 5*       |     | -15*        |     | nS   | [-]  |

| В  | TdCf(MREQf) | Clock Fail to MREQ Fall delay   |          | 85  |          | 70  |          | 60  | 100      | 55  | 200         | 40  | nS   |      |

| 9  | TdCr(MREQr) | Clock Rise to /MREQ Rise delay  |          | 85  |          | 70  |          | 60  |          | 55  |             | 40  | nS   |      |

| 10 | TwMREQh     | /MREQ pulse width (High)        | 110°     |     | 65*      |     | 45**     |     | 30*      |     | 10*         | -10 | nS   | [3]  |

| 11 | TwMREQI     | /MREQ pulse width (low)         | 220°     |     | 132*     |     | 100*     |     | 75*      |     | 25*         |     | nS   | [3]  |

| 12 | TdCf(MERQr) | Clock Fall to /MREQ Rise delay  |          | 85  |          | 70  |          | 60  |          | 55  |             | 40  | nS   | [-]  |

| 13 | TdCf(RDf)   | Clock Fall to /RD Fall delay    |          | 95  |          | 80  |          | 70  |          | 65  |             | 40  | nS   |      |

| 14 | TdCr(RDr)   | Clock Rise to /RD Rise delay    |          | 85  |          | 70  |          | 60  |          | 55  |             | 40  | nS   |      |

| 15 | TsD(Cr)     | Data setup time to Clock Rise   | 35       |     | 30       |     | 30       |     | 25       |     | 12          |     | nS   |      |

| 16 | ThD(RDr)    | Data hold time after /RD Rise   | 0        | -   | 0        |     | 0        |     | 0        |     | 0           |     | nS   |      |

| 17 | TsWAIT(Cf)  | WAIT setup time to Clock Fall   | 70       |     | 60       |     | 50       |     | 20       |     | 7.5         |     | nS   |      |

| 18 | ThWAIT(Cf)  | WAIT hold time after Clock Fall | 10       |     | 10       |     | 10       |     | 10       |     | 10          |     | nS   |      |

| 19 | TdCr(M1f)   | Clock Rise to /M1 Fall delay    |          | 100 |          | 80  |          | 70  |          | 65  |             | 45  | nS   |      |

| 20 | TdCr(M1r)   | Clock Rise to /M1 Rise delay    |          | 100 |          | 80  |          | 70  |          | 65  |             | 45  | nS   |      |

|    | TdCr(RFSHt) | Clock Rise to /RFSH Fall delay  |          | 130 |          | 110 |          | 95  |          | 80  |             | 60  | nS   |      |

|    | TdCr(RFSHr) | Clock Rise to /RFSH Rise delay  |          | 120 |          | 100 |          | 85  |          | 80  |             | 60  | nS   |      |

| 23 | TdCf(RDr)   | Clock Fall to /RD Rise delay    |          | 85  |          | 70  |          | 60  |          | 55  |             | 40  | nS   |      |

|    |             | Clock Rise to /RD Fall delay    |          | 85  |          | 70  |          | 60  |          | 55  |             | 40  | nS   |      |

| 25 | TsD(Cf)     | Data setup to Clock Fall during |          |     |          |     |          |     |          |     |             |     |      |      |

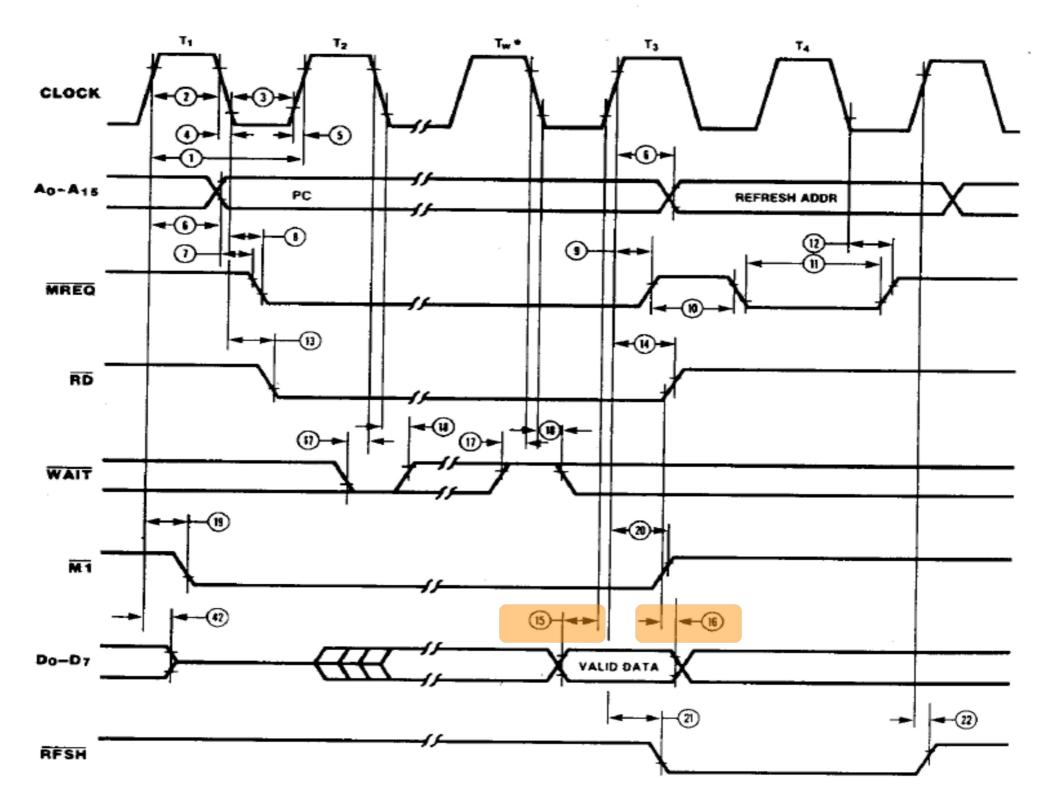

- del Z80 (cartilla)

- Marcados en diagramas de tiempos "CPU Timing", pag. 24

- Valores en sección "AC Characteristics", pag. 35

- de memorias y otros chips

- En las respectivas hojas de datos

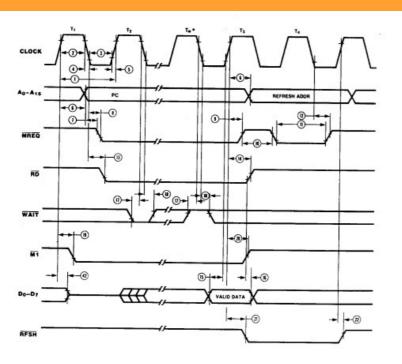

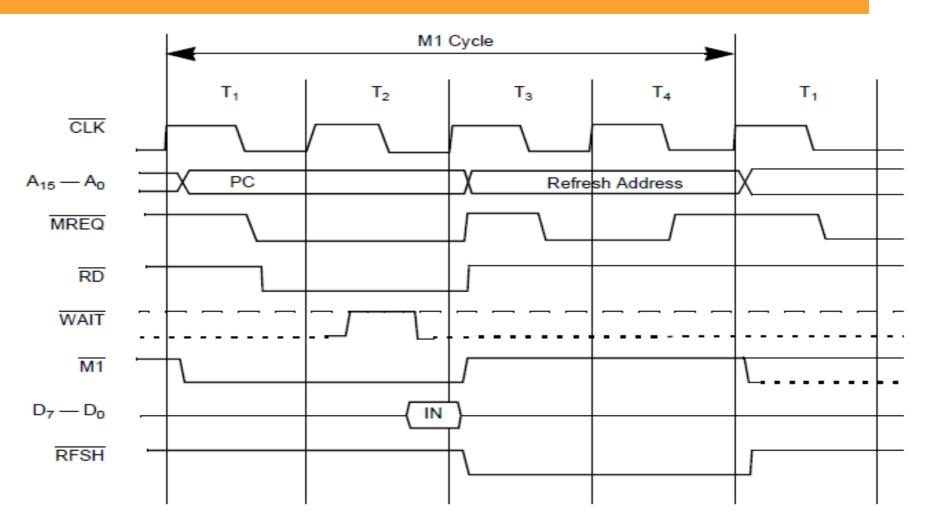

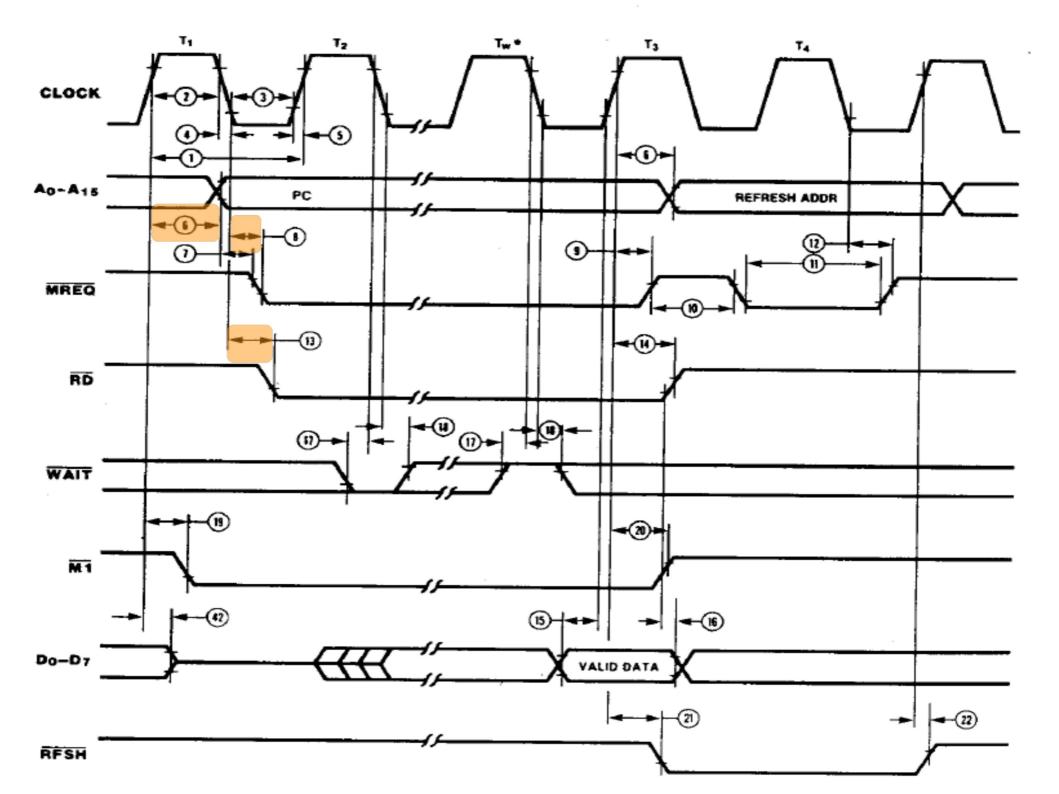

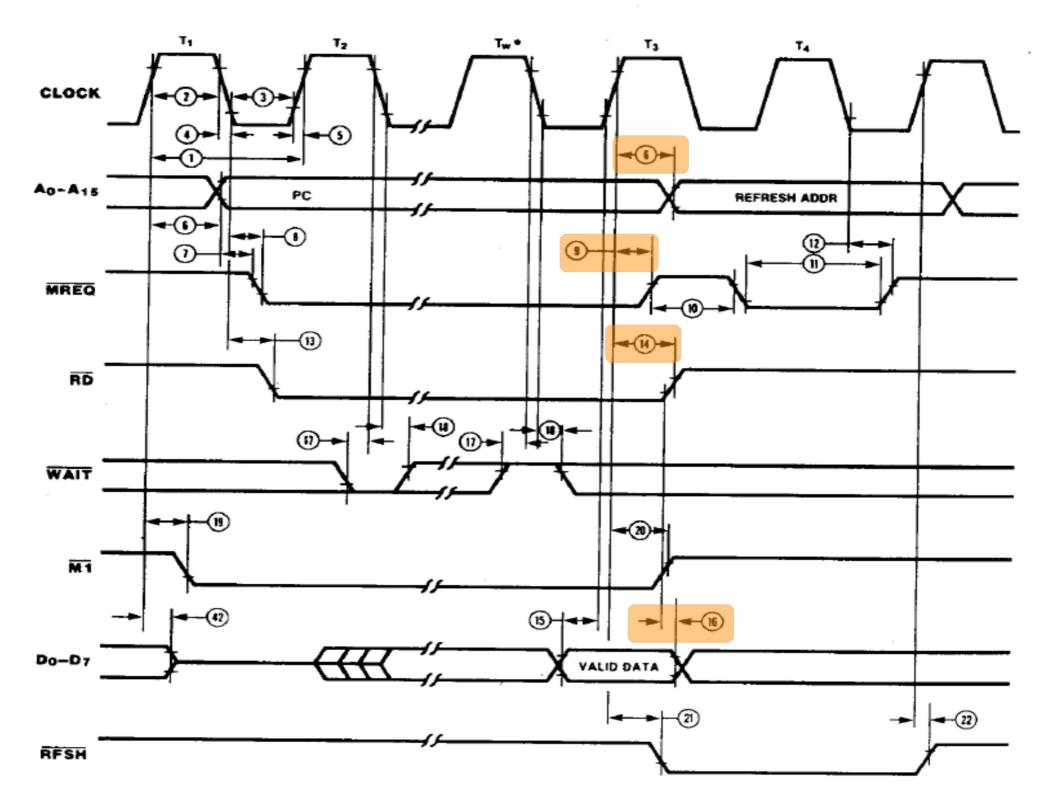

### Ejemplo: Ciclo M1

- Es una lectura:

- requerimientos impuestos por Z80

- t15: Data setup time to Clock ↑ TsD(Cr)

- t16: Data hold time after RD ↑ ThD(RDr)

- Requerimientos y retardos del Z80

- Marcados en diagramas "CPU Timing", pag. 24

- Tabulados en sección "AC Characteristics", pag. 35

- Retardos de memorias y otros chips

- En la respectiva hoja de datos

### Ciclos M1

Figure 5. Instruction Op Code Fetch

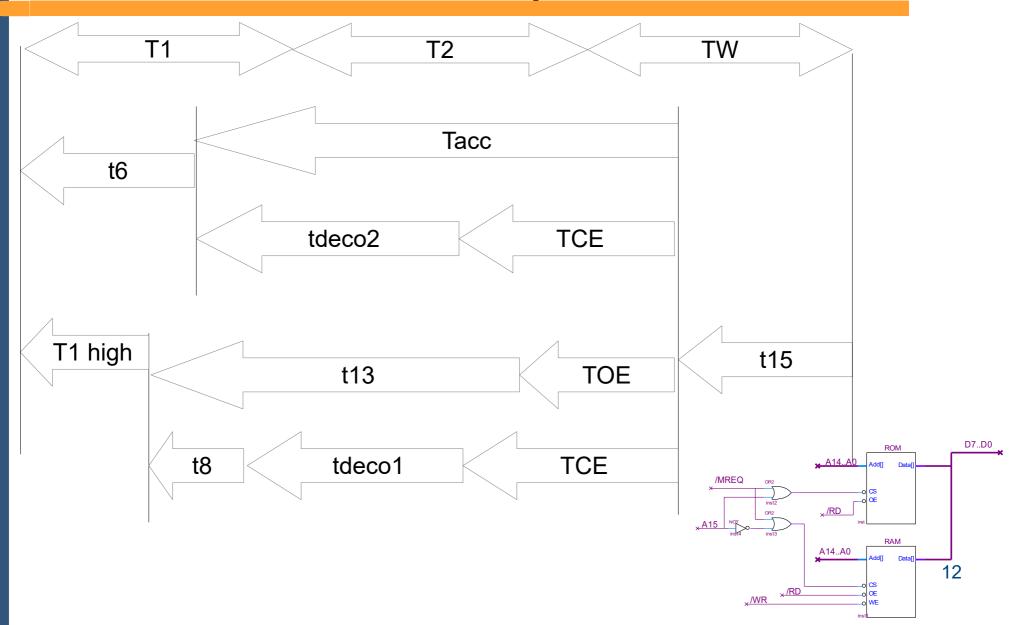

## Ejemplo 32K ROM + 32K RAM

- Retardo decodificación t<sub>deco</sub>

- t<sub>deco1</sub>: desde /MREQ a CS (ej: retardo OR)

- t<sub>deco2</sub>: desde direcciones a CS (ej: retardos NOT + OR)

#### AC CHARACTERISTICS<sup>†</sup> (Z84C00/CMOS Z80 CPU)

$V_{cc}$ =5.0V ± 10%, unless otherwise specified

|    |             |                                |          | *          | *    |       |            |     |          |            |             |     |      |      |

|----|-------------|--------------------------------|----------|------------|------|-------|------------|-----|----------|------------|-------------|-----|------|------|

|    |             |                                | Z84C0004 |            | Z840 | 20006 | Z84C0008   |     | Z84C0010 |            | Z84C0020[1] |     | Unit | Note |

| No | Symbol      | Parameter                      | Min      | Max        | Min  | Max   | Min        | Max | Min      | Max        | Min         | Max |      |      |

| 1  | TcC         | Clock Cycle time               | 250°     | DC         | 162* | DC    | 125*       | DC  | 100*     | DC         | 50°         | DC  | nS   |      |

| 2  | TwCh        | Clock Pulse width (high)       | 110      | DC         | 65   | DC    | 55         | DC  | 40       | DC         | 20          | DC  | nS   |      |

| 3  | TwCl        | Clock Pulse width (low)        | 110      | DC         | 65   | DC    | <b>5</b> 5 | DC  | 40       | DC         | 20          | DC  | nS   |      |

| 4  | TfC         | Clock Fall time                |          | 30         |      | 20    |            | 10  |          | 10         |             | 10  | nS   |      |

| 5  | TrC         | Clock Rise time                |          | 30         |      | 20    |            | 10  |          | 10         |             | 10  | nS   |      |

|    |             |                                |          |            |      |       |            |     |          |            |             |     |      |      |

| 6  | TdCr(A)     | Address vaild from Clock Rise  | '        | 110        |      | 90    |            | 80  |          | 65         |             | 57  | nS   | [2]  |

| 7  | TdA(MREQf)  | Address valid to /MREQ Fall    | 65*      |            | 35*  |       | 20*        |     | 5*       |            | -15*        |     | пS   |      |

| 8  | TdCf(MREQf) | Clock Fall to MREQ Fall delay  |          | 85         |      | 70    |            | 60  |          | 55         |             | 40  | nS   |      |

| 9  | TdCr(MREQr) | Clock Rise to /MREQ Rise delay |          | 85         |      | 70    |            | 60  |          | 55         |             | 40  | nS   |      |

| 10 | TwMREQh     | /MREQ pulse width (High)       | 110*     |            | 65*  |       | 45**       |     | 30⁴      |            | 10°         |     | nS   | [3]  |

| _  |             |                                |          |            |      |       |            |     |          |            |             |     |      |      |

| 11 | TwMREQ!     | /MREQ pulse width (low)        | 220*     |            | 132* |       | 100*       |     | 75°      |            | 25*         |     | nS   | [3]  |

| 12 | TdCf(MERQr) | Clock Fall to MREQ Rise delay  |          | 85         |      | 70    |            | 60  |          | <b>5</b> 5 |             | 40  | nS   |      |

| 13 | TdCf(RDf)   | Clock Fall to /RD Fall delay   |          | 95         |      | 80    |            | 70  |          | 65         |             | 40  | nS   |      |

| 14 | TdCr(RDr)   | Clock Rise to /RD Rise delay   |          | <b>8</b> 5 |      | 70    |            | 60  |          | <b>5</b> 5 |             | 40  | n\$  |      |

| 15 | TsD(Cr)     | Data setup time to Clock Rise  | 35       |            | 30   |       | 30         |     | 25       |            | 12          |     | nS   |      |

|    |             |                                |          |            |      |       |            |     |          |            |             |     |      |      |

## Ejemplo: Ciclo M1 Setup

- El tiempo de setup efectivo debe ser mayor que t15 requerido

- (1) Tiempo de acceso desde direcciones

```

T1 + T2 + nTw - t6max - tacc > t15min

```

• (2) Tiempo desde OE a datos válidos

```

T1low + T2 + nTw - t13max - toe > t15min

```

- (3) Tiempo desde CE a datos válidos

- (3.1) por MREQ

```

T1low + T2 + nTw - t8max - tdeco - tce > t15min

```

- (3.2) por direcciones

```

T1 + T2 + nTw - t6max - tdeco - tce > t15min

```

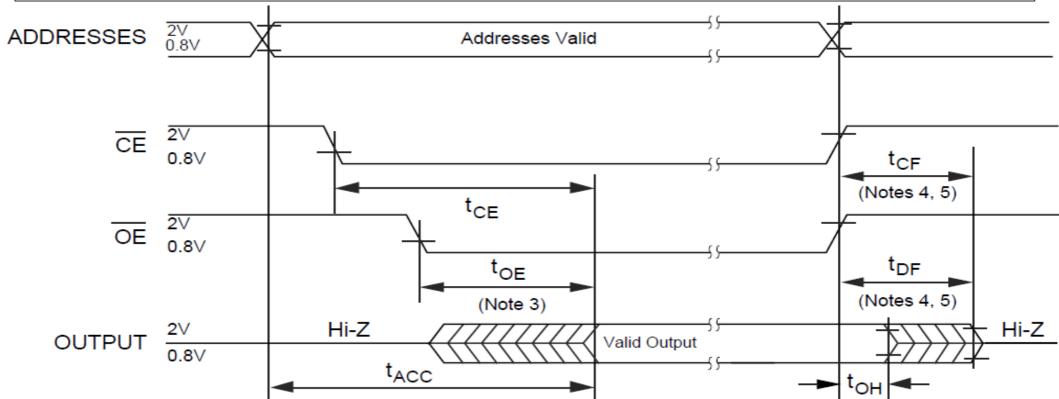

AC Electrical Characteristics Over Operating Range with V<sub>PP</sub> = V<sub>CC</sub>

| Symbol                      | Parameter                                                            | 9   | 0   | 1   | 20  | 150 |     | 200 |     | Units |

|-----------------------------|----------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-------|

|                             |                                                                      | Min | Max | Min | Max | Min | Max | Min | Max |       |

| t <sub>ACC</sub>            | Address to Output Delay                                              |     | 90  |     | 120 |     | 150 |     | 200 | ns    |

| t <sub>CE</sub>             | CE to Output Delay                                                   |     | 90  |     | 120 |     | 150 |     | 200 | ns    |

| t <sub>OE</sub>             | OE to Output Delay                                                   |     | 50  |     | 50  |     | 50  |     | 50  | ns    |

| t <sub>CF</sub><br>(Note 2) | CE High to Output Float                                              |     | 30  |     | 30  |     | 45  |     | 55  | ns    |

| t <sub>DF</sub><br>(Note 2) | OE High to Output Float                                              |     | 35  |     | 35  |     | 45  |     | 55  | ns    |

| t <sub>OH</sub><br>(Note 2) | Output Hold from Addresses,<br>CE or OE,<br>Whichever Occurred First | 0   |     | 0   |     | 0   |     | 0   |     | ns    |

# Ejemplo: Ciclo M1 Setup

## Ejemplo: Ciclo M1 Hold

- t16 requerido desde subida de RD

- Si datos dejan de estar válidos por:

- (1) Cambio en direcciones

```

t6 + Toh_mem - t14 > t16min

```

(2) Cambio en RD

```

Toh > t16min

```

- (3) Cambio en CS

- (3.1) por MREQ

```

t9 + tdeco + Toh - t14 > t16min

```

- (3.2) por direcciones

```

t6 + tdeco + Toh - t14 > t16min

```

Parámetros deben cumplir ecuac., no se arregla insertando Tw.

#### AC CHARACTERISTICS<sup>†</sup> (Z84C00/CMOS Z80 CPU)

$V_{cc}$ =5.0V ± 10%, unless otherwise specified

| , CC | -0.01 1 1070,   | diffess officialise specified   |          |          |      |     |          |     |             |            |             |            |      |     |

|------|-----------------|---------------------------------|----------|----------|------|-----|----------|-----|-------------|------------|-------------|------------|------|-----|

|      |                 |                                 | Z84C0004 |          |      |     | Z84C0008 |     | Z84C0010    |            | Z84C0020[1] |            | Unit | Not |

| No   | Symbol          | Parameter                       | Min      | Max      | Min  | Мах | Min      | Мах | Min         | Max        | Min         | Мах        |      | -   |

| 1    | TcC             | Clock Cycle time                | 250*     | DC       | 162* | DC  | 125*     | DC  | 100*        | DC         | 50 <b>*</b> | DC         | nS   |     |

| 2    | TwCh            | Clock Pulse width (high)        | 110      | DC       | 65   | DC  | 55       | DC  | 40          | DC         | 20          | DC         | nS   |     |

| 3    | TwCl            | Clock Pulse width (low)         | 110      | DC       | 65   | DC  | 55       | DC  | 40          | DC         | 20          | DC         | nS   |     |

| 4    | TfC             | Clock Fall time                 |          | 30       |      | 20  |          | 10  |             | 10         |             | 10         | nS   |     |

| 5    | TrC             | Clock Rise time                 |          | 30       |      | 20  |          | 10  |             | 10         |             | 10         | nS   |     |

|      |                 |                                 |          |          |      | •   |          |     |             |            |             |            |      |     |

| 6    | TdCr(A)         | Address vaild from Clock Rise   | _        | 110      |      | 90  |          | 80  |             | 65         |             | 57         | nS   | [2] |

| 7    | TdA(MREQf)      | Address valid to /MREQ Fall     | 65*      |          | 35*  |     | 20*      |     | 5*          |            | -15*        |            | nS   |     |

| 8    | TdCf(MREQf)     | Clock Fall to MREQ Fall delay   |          | 85       |      | 70  |          | 60  |             | <b>5</b> 5 |             | <b>4</b> 0 | nS   |     |

| 9    | TdCr(MREQr)     | Clock Rise to /MREQ Rise delay  | $\star$  | 85       |      | 70  |          | 60  |             | 55         |             | 40         | nS   |     |

| 10   | <b>TwMREQ</b> h | /MREQ pulse width (High)        | 110      | •        | 65*  |     | 45**     |     | 30*         |            | 10*         |            | nS   | [3] |

|      | <u> </u>        |                                 |          | <u> </u> |      |     |          | •   |             |            |             |            |      |     |

| 11   | TwMREQ          | MREQ pulse width (low)          | 220      | •        | 132  | •   | 1001     | ·   | <b>75</b> * |            | 25*         |            | nS   | [3] |

| 12   | TdCf(MERQr)     | Clock Fall to /MREQ Rise delay  |          | 85       |      | 70  |          | 60  |             | <b>5</b> 5 |             | 40         | nS   |     |

| 13   | TdCf(RDf)       | Clock Fall to /RD Fall delay    |          | 95       |      | 80  |          | 70  |             | 65         |             | 40         | nS   |     |

| 14   | TdCr(RDr)       | Clock Rise to /RD Rise delay    |          | 85       |      | 70  |          | 60  |             | 55         |             | 40         | nS   |     |

| 15   | TsD(Cr)         | Data setup time to Clock Rise   | 35       |          | 30   |     | 30       |     | 25          |            | 12          |            | nS   |     |

|      |                 |                                 |          |          |      |     |          |     |             |            |             |            |      |     |

| 16   | ThD(RDr)        | Data hold time after /RD Rise 💢 | 0        |          | 0    |     | 0        |     | 0           |            | 0           |            | nS   |     |

## Ejemplo: Ciclo Escritura Prueba Final 2014 – Ej. 1

- Data Setup (TDS):

- T1L + T2 + nTW + T3H + min {( t12(min) + tor(min) ) , t32(min)} t53(max)

- Mayor o igual al TDS mínimo requerido por la memoria